# DATA BOOK

# Z8 MICROCOMPUTER FAMILY

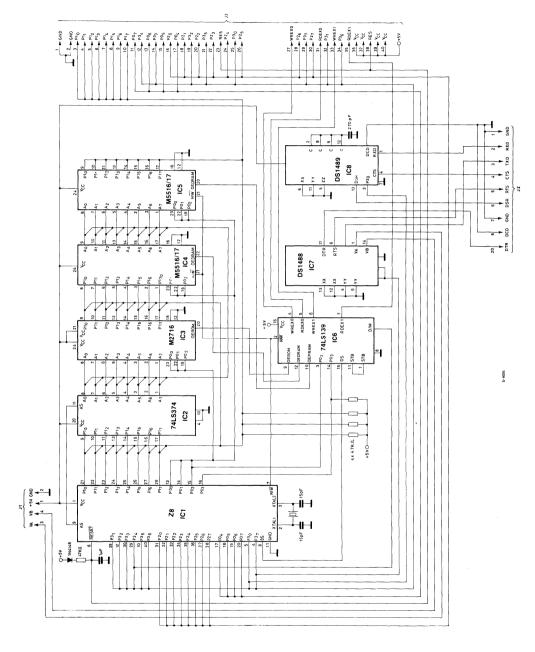

3<sup>rd</sup> EDITION \MAY 1986

The Z8 2K ROM single chip microcomputer produced by SGS using NMOS technology

Automatic electrical test of a VLSI device in the SGS Agrate facility

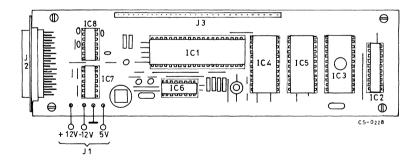

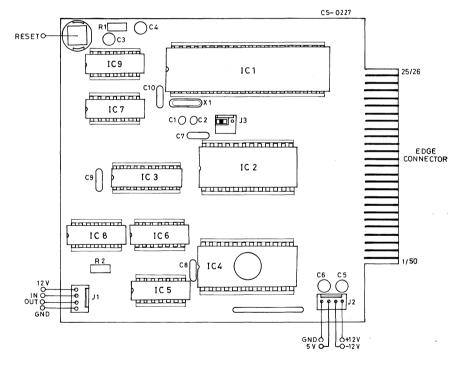

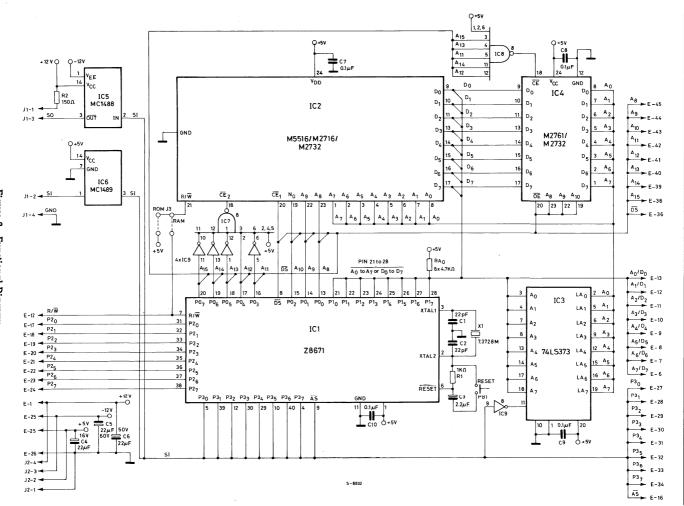

Application board using Z8671 tiny Basic microcomputer

# **Contents**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ?age                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| SGS: an introduction                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3                                                 |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                                                 |

| Cross Reference                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 9                                               |

| Part Number Identification                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                 |

| Datasheets                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13                                                |

| NMOS Family  — Z8601/L  — Z8611/L  — Z8621/L  — Z8671  — Z8681/L  — Z8682/L  — Z8682/L  — Z8684/L  — Z86E11  — Z86E21                                                                                                                                                                                                                                                                                                                                       | 35<br>57<br>79<br>103<br>103<br>103<br>129<br>155 |

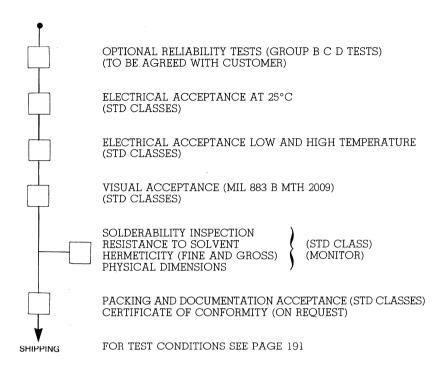

| Reliability Informations                                                                                                                                                                                                                                                                                                                                                                                                                                    | 187                                               |

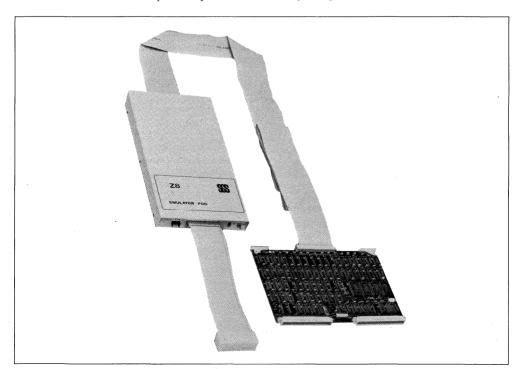

| Development Products  — General Purpose Fundation Module for MCU Emulation  — Z8 Emulation and Development Package  — Z8 Emulation and Development Package for IBM compatible Personal Computers .                                                                                                                                                                                                                                                          | 199<br>203                                        |

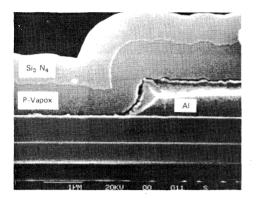

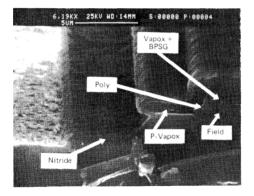

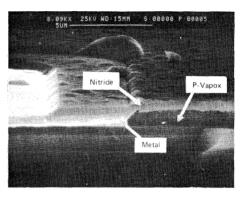

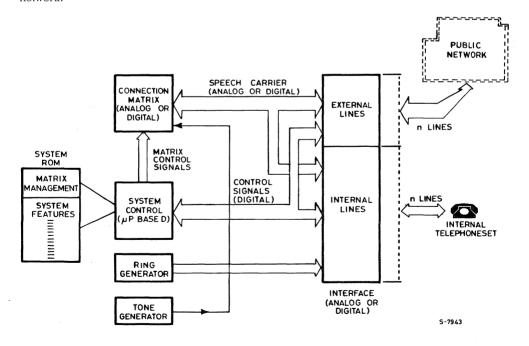

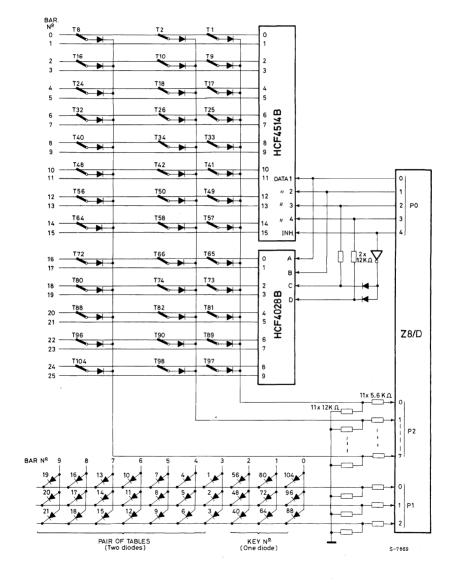

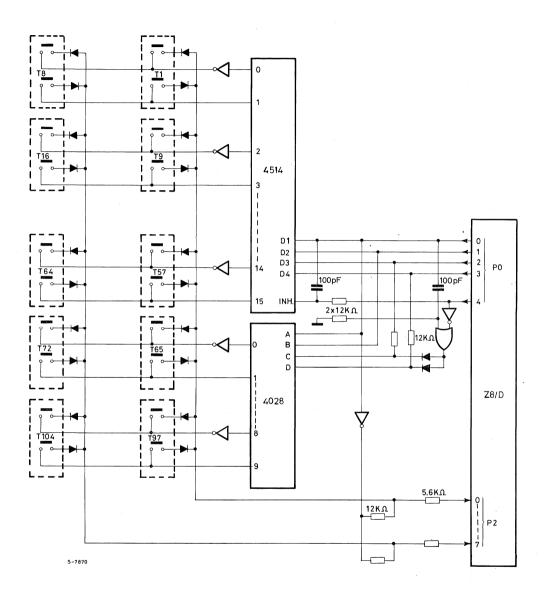

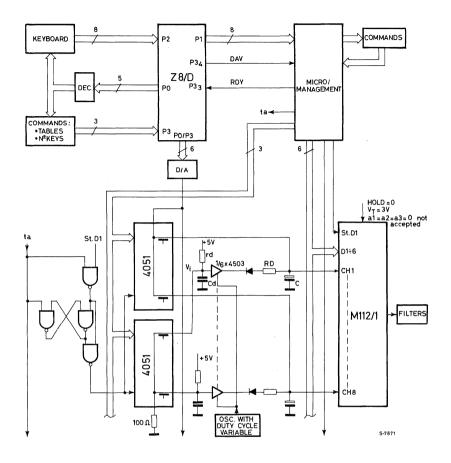

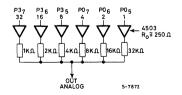

| Technical and Application Notes  — Double Layer P-Vapox and SI <sub>3</sub> N <sub>4</sub> Glass Passivation — PMZ8: Z8681 in Single Board Computer Application — Single Board Computer Using Z8671 — Z8 in Electronic Private Automated Branch Exchange (EPABX 2 Ext./8 Int. Lines) — Using Z8 MCU in Keyboard Controller — Z8 MCU in Dynamic Keyboard — Comparison of Z8611, 8051 and MC6801 Microcomputer — A Programmer's Guide to the Z8 Microcomputer | 213<br>215<br>219<br>227<br>237<br>241<br>251     |

# **Identity**

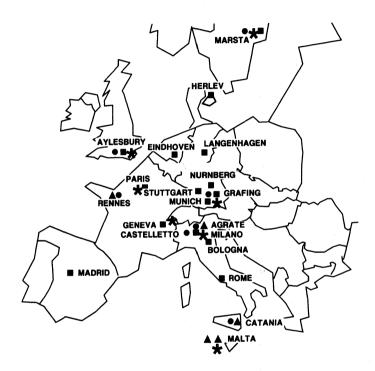

Late in 1957, SGS was founded around a team of researchers who were already carrying out pioneer work in the field of semiconductors. From that small nucleus, the company has evolved into a Group of Companies, operating on a worldwide basis as a broad range semiconductor producer, with billings over 300 million dollars and employing over 9500 people.

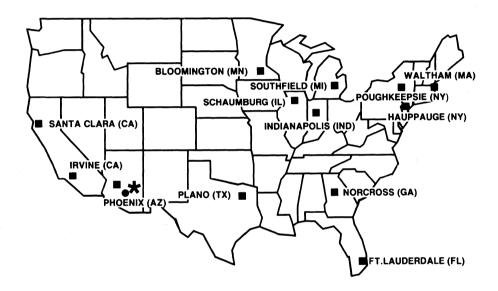

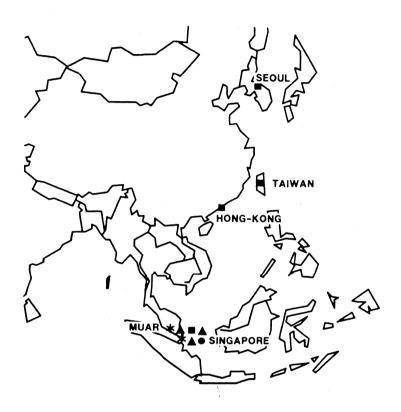

The SGS Group of Companies has now reached a total of 11 subsidiaries, located in Brazil, France, Germany, Italy, Malta, Malaysia, Singapore, Sweden, Switzerland, United Kingdom and the USA.

To go with its logo, the company takes the motto "Technology and Service", underlining the accent given to the development of state-of-the-art technologies and the corporate commitment to offer customers the best quality and service in the industry.

# **SGS Locations - Europe**

- \* HEADQUARTERS

- **A FACTORIES**

- SALES OFFICES

- DESIGN CENTERS

# **SGS Locations - North America**

- \* HEADQUARTERS

- SALES OFFICES

- DESIGN CENTERS

# **SGS Locations - Asia/Pacific**

- \* HEADQUARTERS

- **▲ FACTORIES**

- **SALES OFFICES**

- DESIGN CENTERS

# **Overview**

# Z8\* Family

The Z8 microcomputer family offers the most sophisticated processing capability available on a single chip. As an extension of earlier generations of microcomputers, the Z8 family provides standard on-chip functions, such as:

- 2K, 4K or 8K bytes of ROM

- 144 or 256 8-bit registers

- 32 lines of programmable I/O

- Clock oscillator

In addition, the Z8 Family offers advanced on-chip features, including:

- Two counter/timers

- Six vectored interrupts

- UART for serial I/O communication

- Stack functions

- Power-down option

- TTL compatibility

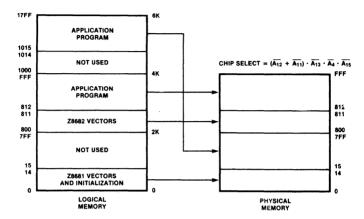

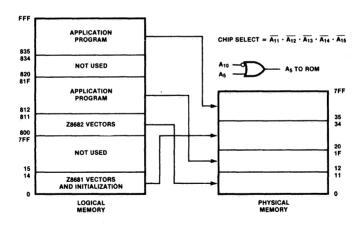

The Z8 microcomputer family is expandable off-chip to provide an additional 62K bytes of program memory and 62K bytes of data memory for the 2K-byte ROM version, an additional 60K bytes of program memory and 60K bytes of data memory for the 4K-byte ROM version and an additional 56K bytes of program memory and 56K bytes of data memory for the 8K-byte ROM version. The interface to external memory is accomplished through one, one and onehalf, or two of the 8-bit I/O ports, depending on the number of address bits required for the external functions. The Z-BUS\* protocol allows easy interface to external functions including peripheral

The Z8 family challenges the "multi-chip solution" design currently implemented by general-purpose microprocessors. Designs based on Z8 family microcomputers offer a minimum chip-count configuration that can easily be expanded to meet requirements for enhancement options and for future

improvements.

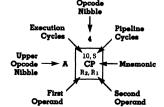

Optimized Instruction Set. The instruction set of the Z8 family is optimized for high-code density and reduced execution time. This feature is supported by a "working register area" concept that uses short (4-bit) register addresses. The general-purpose registers can be used as accumulators, as address pointers for indirect addressing, as index registers, or for implementing an on-chip stack.

The 47 instruction types and six addressing modes—together with the ability to operate on bits, 4-bit BCD digits, 8-bit bytes, and 16-bit words—offer unique programming

capability and flexibility.

Growing Family. The Z8 microcomputer family is growing to meet the needs of more complex designs. The 8K ROM version, Z8621 completed developed by SGS, offers all the features of the Z8 Family, plus 8K bytes of on-chip ROM and 256-byte register file. The increased ROM and bytes register file allows the designer to take advantage of the code optimization inherent in the Z8 instruction set when using between 2K and 8K bytes at program memory.

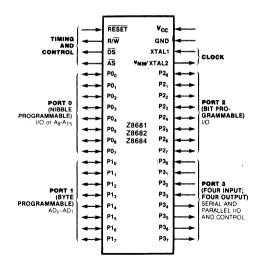

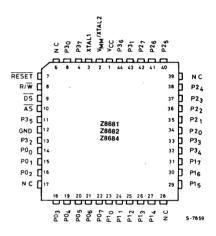

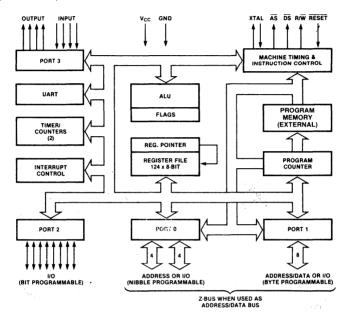

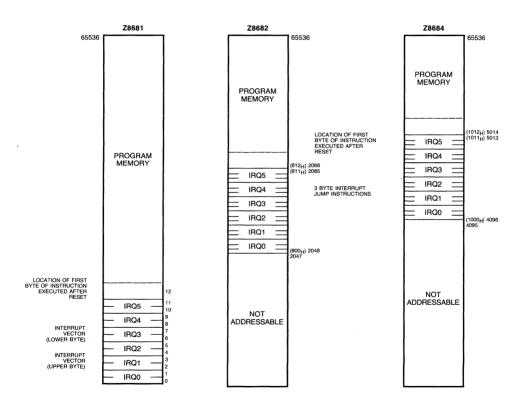

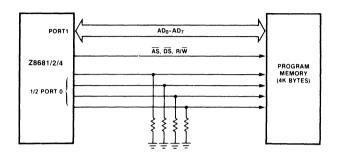

The ROMless microcomputers provide an alternative for designers seeking to take advantage of the on-chip features of the Z8681, Z8682 and Z8684 in applications that require external program memory. A Z8681 microcomputer can be used to control a system that addresses up to 128K bytes of on-chip memory, a Z8682 up to 124K bytes and

Z8684 up to 120K bytes.

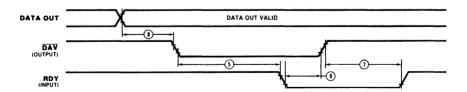

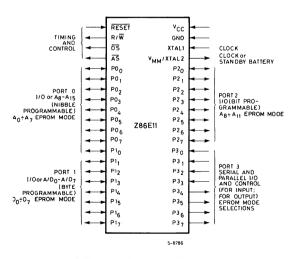

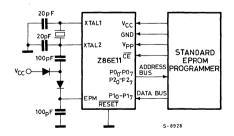

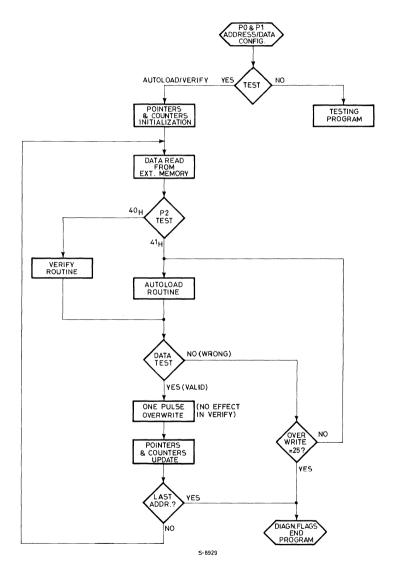

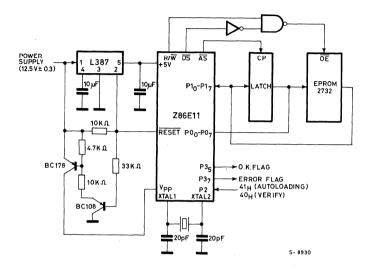

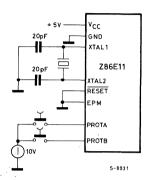

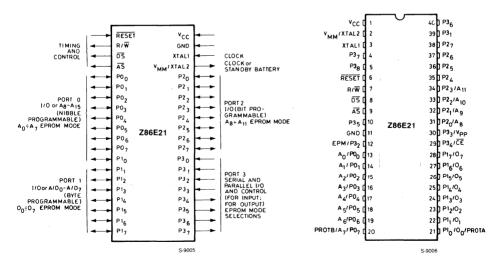

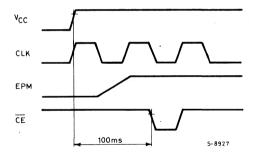

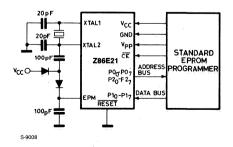

Newly in the Z8 family the 4K and 8K bytes on-chip Eprom Z86E11 and Z86E21, that perform different programming modes, like: Eprom-like, using standard eprom programmer; Self-programming, during normal microcomputer operation and time-efficient self-program facility; and integrated programmable Eprom read-out protection.

For there characteristics the Z86E11 and Z86E21 can be considered as low cost development tools for the Z8 microcomputer

family.

Low Power version 80mA current consumption, on all the family will be available.

**Expanded Applications.** The Z8 microcomputer family is finding its way into increasingly sophisticated designs. In addition to the low-end capability applications commonly used with microcomputers, the Z8 family can be used effectively in such applications as:

- Computer peripheral controllers

- Smart terminals

- Dumb terminals

- Telephone switching systems

- Arcade games and intelligent home games

- Process control

- Intelligent instrumentation

- Automotive mechanisms

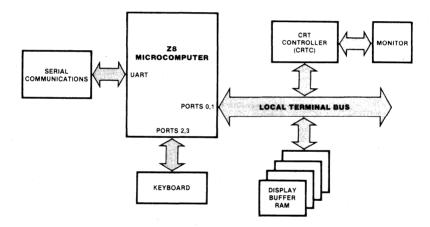

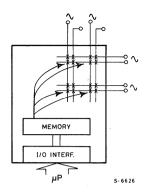

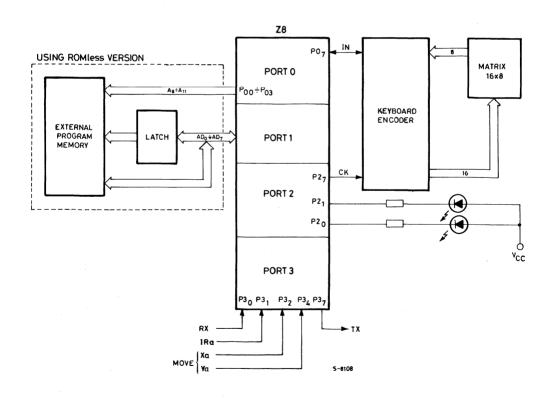

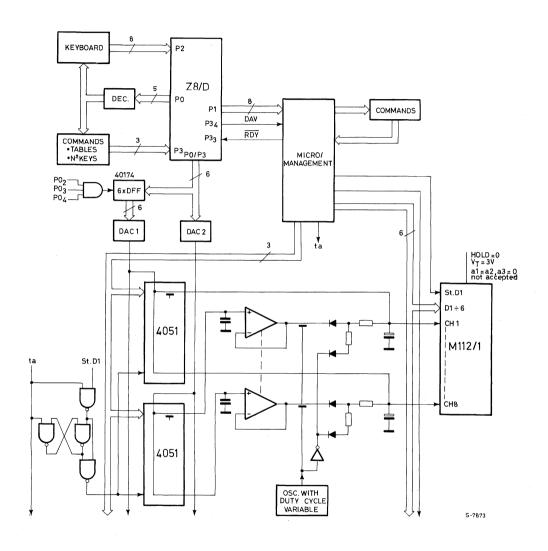

An example of how a Z8 might be used in the design of an intelligent terminal is shown in Figure 1. The features of such a terminal depend on its specific requirements, but it is clear that the Z8 microcomputers offer unprecedented capability and flexibility to the microcomputer designer.

Figure 1. Z8 Based Intelligent Terminal

# **Z8** Cross Reference

|              |                       |                              | su            | FFIX DE       | SCRIP1         | ION      |        |   |             |            |  |

|--------------|-----------------------|------------------------------|---------------|---------------|----------------|----------|--------|---|-------------|------------|--|

|              | BASE PART             | SPEED SUFFIX (MHz)  8.0 12.0 |               |               | PACKAGE SUFFIX |          |        |   | TEMP. SUFFI |            |  |

|              | NUMBER                |                              |               | PL            |                |          |        |   |             | -40/+85°C  |  |

| SGS<br>ZILOG | <b>Z86XX</b><br>Z86XX | *                            | <b>A</b><br>A | <b>В</b><br>Р | <b>F</b>       | <b>D</b> | C<br>V | K | l<br>S      | <b>6</b> E |  |

|       |        |        |        | Γ             | EVICE TYP | Е           |             |                   |                  |

|-------|--------|--------|--------|---------------|-----------|-------------|-------------|-------------------|------------------|

|       | 2K ROM | 4K ROM | 8K ROM | TINY<br>BASIC | ROMLESS   | 4K<br>EPROM | 8K<br>EPROM | 2K PIGGY-<br>BACK | 4K PIGGY<br>BACK |

| SGS   | Z8601  | Z8611  | Z8621  | Z8671         | Z8681/2/4 | Z86E11      | Z86E21      | _                 | _                |

| ZILOG | Z8601  | Z8611  | . —    | Z8671         | Z8681/2/4 | .—          | _           | Z8603RS           | Z8613RS          |

Notes: \* Standard Version no suffix required

na: Not Available

# SGS Part Number Identification

|                      |                                          | example: | Z8621 | A | XX | В | 1 |

|----------------------|------------------------------------------|----------|-------|---|----|---|---|

| Circuit Desig        | nator                                    |          |       |   |    |   |   |

| Speed                |                                          |          |       |   |    |   |   |

| No letter<br>A       | 8.0 MHz<br>12.0                          |          |       |   |    |   |   |

| ROM Content          | t where requests                         |          |       |   |    |   |   |

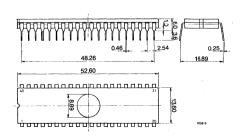

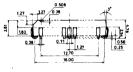

| Package              |                                          |          |       |   |    |   |   |

|                      | ded Chip Carrier<br>eadless Chip Carrier |          |       |   |    |   |   |

| Temperature          | Range                                    |          |       |   |    |   |   |

| 1 0 to + 6 - 40 to + |                                          |          |       |   |    |   |   |

**D**atasheets

# **Z8 2K ROM Microcomputer**

- Complete microcomputer, 2K bytes of ROM, 128 bytes of RAM, 32 I/O lines, and up to 62K bytes addressable external space each for program and data memory.

- 144-byte register file, including 124 general-purpose registers, four I/O port registers, and 16 status and control registers.

- Minimum instruction execution time 1 μs, at 12 MHz.

- Vectored, priority interrupts for I/O, counter/timers, and UART.

- Full-duplex UART and two programmable 8-bit counter/timers, each with a 6-bit programmable prescaler.

- Register Pointer so that short, fast instructions can access any of nine working register groups in 1 μs.

- On-chip oscillator that accepts crystal or external clock drive.

- Low-power standby option which retains contents of general-purpose registers.

- Single +5 V power supply—all pins TTLcompatible.

- Low Power version (Z8601L):

- Available 8 MHz

- Current consumption 80 mA

- Available in 8 and 12 MHz versions.

### General Description

The Z8601 microcomputer introduces a new level of sophistication to single-chip architecture. Compared to earlier single-chip microcomputers, the Z8601 offers faster execution; more efficient use of memory; more sophisticated interrupt, input/output and bit-manipulation capabilities; and easier system expansion.

Under program control, the Z8601 can be

tailored to the needs of its user. It can be configured as a stand-alone microcomputer with 2K bytes of internal ROM, a traditional microprocessor that manages up to 124K bytes of external memory, or a parallel-processing element in a system with other processors and peripheral controllers linked by the Z-BUS. In all configurations, a large number of pins remain available for I/O.

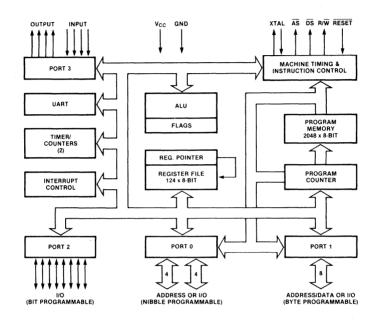

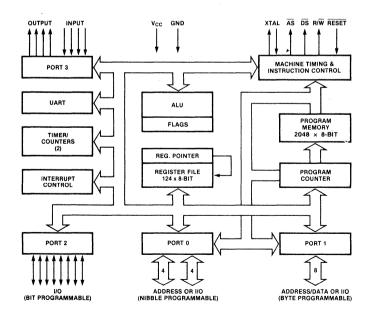

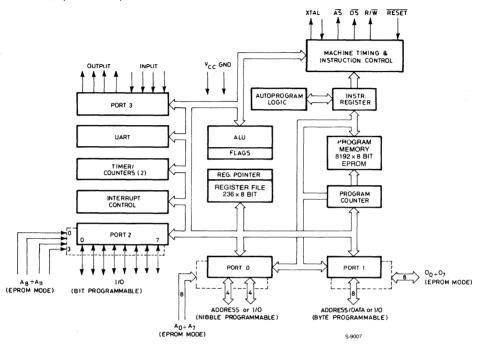

Figure 1. Logic Functions

#### General Description (Continued)

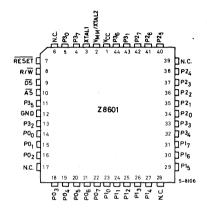

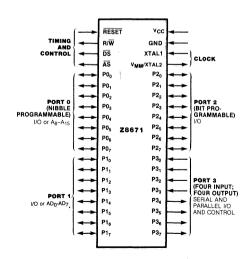

Figure 2. Pin Configuration

N.C.=NO CONNECTION

Figure 2a. Chip Carrier Pin Configuration

#### Architecture

Z8601 architecture is characterized by a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features that are helpful in many applications.

Microcomputer applications demand powerful I/O capabilities. The Z8601 fulfills this with 32 pins dedicated to input and output. These lines are grouped into four ports of eight lines each and are configurable under software control to provide timing, status signals, serial or parallel I/O with or without handshake, and an address/data bus for interfacing external memory.

Because the multiplexed address/data bus is merged with the I/O-oriented ports, the Z8601 can assume many different memory and I/O configurations. These configurations range from a self-contained microcomputer

to a microprocessor that can address 124K bytes of external memory.

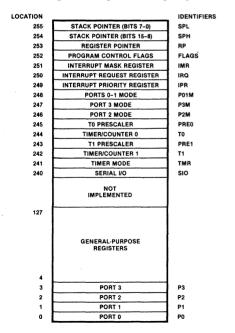

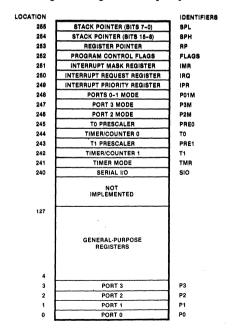

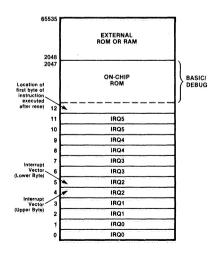

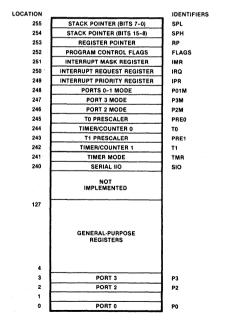

Three basic address spaces are available to support this wide range of configurations: program memory (internal and external), data memory (external) and the register file (internal). The 144-byte random-access register file is composed of 124 general-purpose registers, four I/O port registers, and 16 control and status registers.

To unburden the program from coping with real-time problems such as serial data communication and counting/timing, an asynchronous receiver/transmitter (UART) and two counter/timers with a large number of user-selectable modes are offered on-chip. Hardware support for the UART is minimized because one of the on-chip timers supplies the bit rate.

#### Architecture (Continued)

Figure 3. Block Diagram

#### Pin Description

$\overline{\text{AS}}$ . Address Strobe (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Addresses output via Port 1 for all external program or data memory transfers are valid at the trailing edge of  $\overline{\text{AS}}$ . Under program control,  $\overline{\text{AS}}$  can be placed in the high-impedance state along with Ports 0 and 1, Data Strobe and Read/Write.

**DS.** Data Strobe (output, active Low). Data Strobe is activated once for each external memory transfer.

**P0<sub>0</sub>-P<sub>7</sub>.** I/O Port Lines (input/output, TTL compatible). 8 lines Nibble Programmable that can be configured under program control for I/O or external memory interface.

**Pl<sub>0</sub>-Pl<sub>7</sub>.** I/O Port Lines (input/output, TTL compatible). 8 lines Byte Programmable that can be configured under program control for I/O or multiplexed address  $(A_0-A_7)$  and data  $(D_0-D_7)$  lines used to interface with program/data memory.

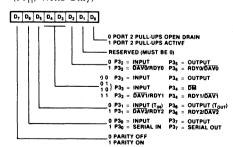

**P2<sub>0</sub>-P2<sub>7</sub>.** I/O Port Lines (input/output, TTL compatible). 8 lines Bit Programmable. In addition they can be configured to provide open-drain outputs.

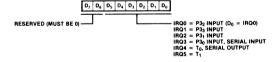

**P3<sub>0</sub>-P3<sub>4</sub>.** Input Port Lines (TTL compatible). They can also configured as control lines.

**P3<sub>5</sub>-P3<sub>7</sub>.** Output Port Lines (TTL compatible). They can also configured as control lines.

# \$\$\$ Z8601/L

#### Pin Descriptions (Continued)

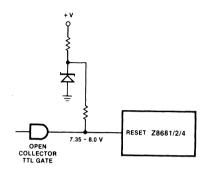

**RESET.** Reset (input, active Low). RESET initializes the Z8601. When RESET is deactivated, program execution begins from internal program location 000C<sub>H</sub>.

$\mathbf{R}/\overline{\mathbf{W}}$ . Read/Write (output). R/ $\overline{\mathbf{W}}$  is Low when the Z8601 is writing to external program or data memory.

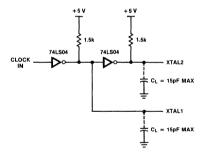

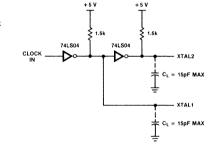

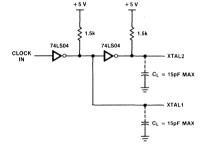

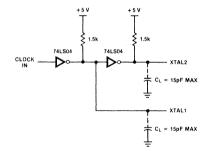

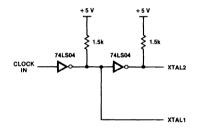

**XTAL1, XTAL2.** Crystal 1, Crystal 2 (time-base input and output). These pins connect a parallel-resonant crystal (8 or 12 MHz maximum) or an external single-phase clock (8 or 12 MHz maximum) to the on-chip clock oscillator and buffer.

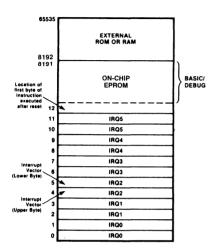

#### **Address Spaces**

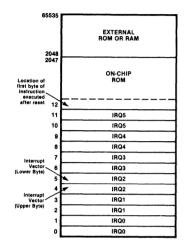

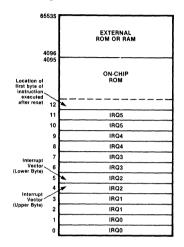

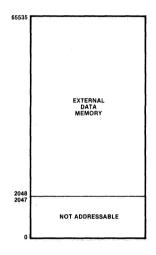

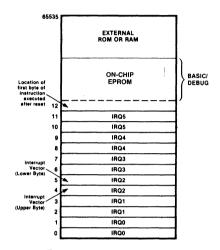

**Program Memory.** The 16-bit program counter addresses 64K bytes of program memory space. Program memory can be located in two areas: one internal and the other external (Figure 4). The first 2048 bytes consist of on-chip mask-programmed ROM. At addresses 2048 and greater, the Z8601 executes external program memory fetches.

The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts.

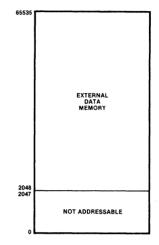

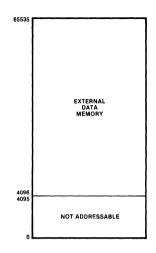

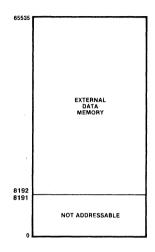

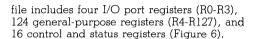

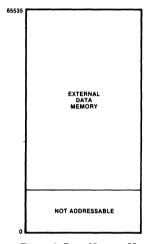

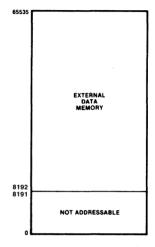

**Data Memory.** The Z8601 can address 62K bytes of external data memory beginning at locations 2048 (Figure 5). External data memory may be included with or separated from the external program memory space.  $\overline{\rm DM}$ , an optional I/O function that can be programmed to appear on pin P34, is used to distinguish between data and program memory space.

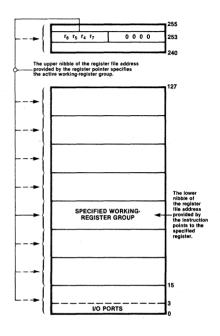

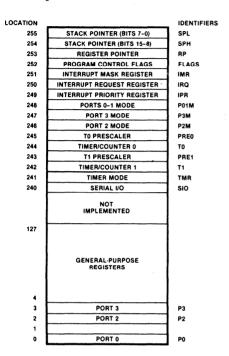

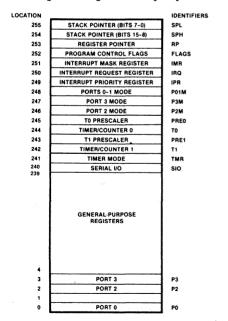

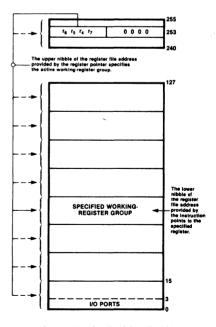

Register File. The 144-byte register file includes four I/O port registers (R0-R3), 124

general-purpose registers (R4-R127) and 16 control and status registers (R240-R255). These registers are assigned the address locations shown in Figure 6.

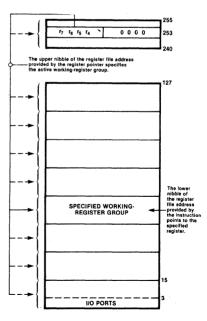

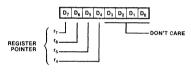

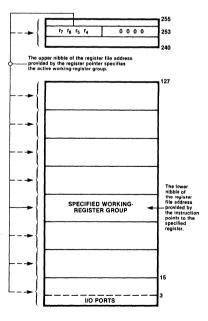

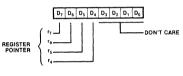

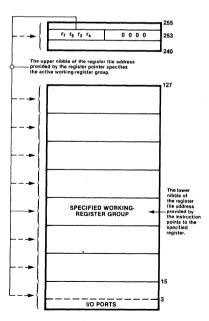

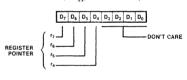

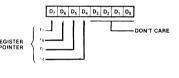

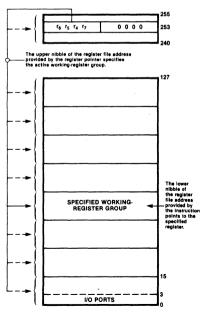

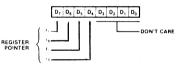

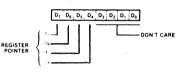

Z8601 instructions can access registers directly or indirectly with an 8-bit address field. The Z8601 also allows short 4-bit register addressing using the Register Pointer (one of the control registers). In the 4-bit mode, the register file is divided into nine working-register groups, each occupying 16 contiguous locations (Figure 7). The Register Pointer addresses the starting location of the active working-register group.

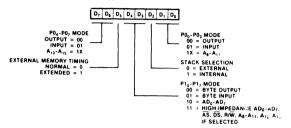

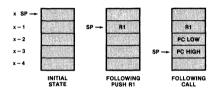

**Stacks.** Either the internal register file or the external data memory can be used for the stack. A 16-bit Stack Pointer (R254 and R255) is used for the external stack, which can reside anywhere in data memory between locations 2048 and 65535. An 8-bit Stack Pointer (R255) is used for the internal stack that resides within the 124 general-purpose registers (R4-R127).

#### Address Spaces (Continued)

Figure 4. Program Memory Map

Figure 6. The Register File

Figure 5. Data Memory Map

Figure 7. The Register Pointer

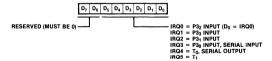

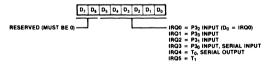

#### Serial Input/Output

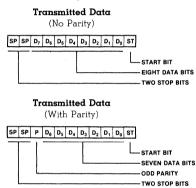

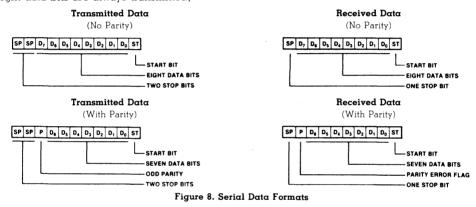

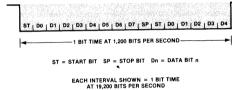

Port 3 lines P3<sub>0</sub> and P3<sub>7</sub> can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/ transmitter operation. The bit rate is controlled by Counter/Timer 0, with a maximum rate of 62.5K bits/second for 8 MHz and 94.8K bits/second for 12 MHz.

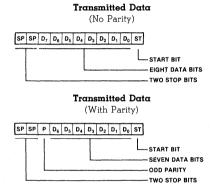

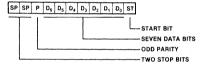

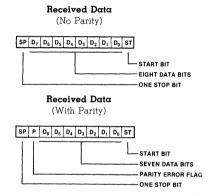

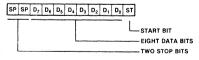

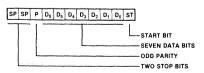

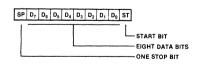

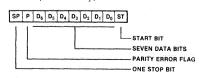

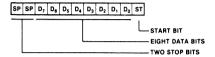

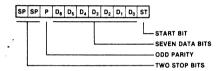

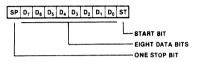

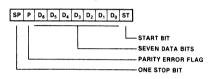

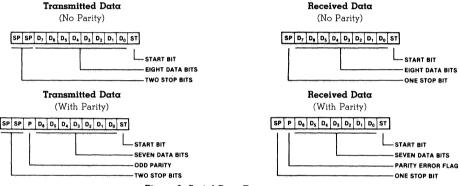

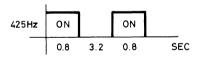

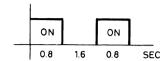

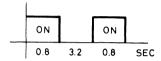

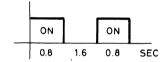

The Z8601 automatically adds a start bit and two stop bits to transmitted data (Figure 8). Odd parity is also available as an option.

Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ<sub>4</sub>) is generated on all transmitted characters.

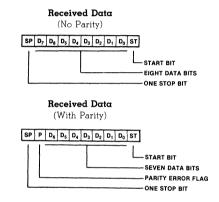

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ<sub>3</sub> interrupt request.

Figure 8. Serial Data Formata

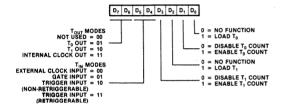

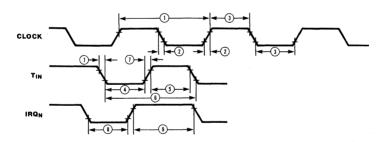

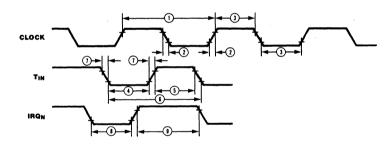

#### Counter/Timers

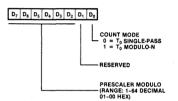

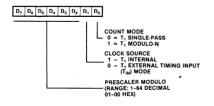

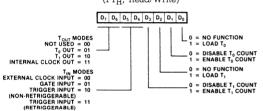

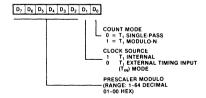

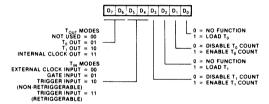

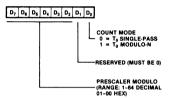

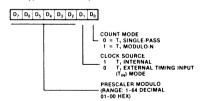

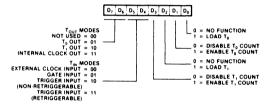

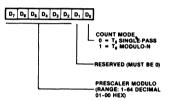

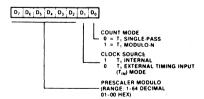

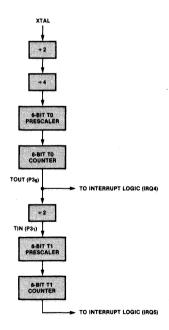

The Z8601 contains two 8-bit programmable counter/timers ( $T_0$  and  $T_1$ ), each driven by its own 6-bit programmble prescaler. The  $T_1$  prescaler can be driven by internal or external clock sources; however, the  $T_0$  prescaler is driven by the internal clock only.

The 6-bit prescalers can divide the input frequency of the clock source by any number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of count, a timer interrupt request—IRQ<sub>4</sub> (T<sub>0</sub>) or IRQ<sub>5</sub> (T<sub>1</sub>)—is generated.

The counters can be started, stopped, restarted to continue, or restarted from the initial value. The counters can also be programmed to stop upon reaching zero (single-pass mode) or to automatically reload

the initial value and continue counting (modulo-n continuous mode). The counters, but not the prescalers, can be read any time without disturbing their value or count mode.

The clock source for  $T_1$  is user-definable and can be the internal microprocessor clock (4 MHz maximum for the 8 MHz device and 6 MHz maximum for the 12 MHz device) divided by four, or an external signal input via Port 3. The Timer Mode register configures the external timer input as an external clock (1 MHz maximum), a trigger input that can be retriggerable or nonretriggerable, or as a gate input for the internal clock. The counter/timers can be porogrammably cascaded by connecting the  $T_0$  output to the input of  $T_1$ . Port 3 line P36 also serves as a timer output (Tour) through which  $T_0$ ,  $T_1$  or the internal clock can be output.

#### I/O Ports

The Z8601 has 32 lines dedicated to input and output. These lines are grouped into four ports of eight lines each and are configurable as input, output or address/data. Under software control, the ports can be programmed to provide address outputs, timing, status signals, serial I/O, and parallel I/O with or without handshake. All ports have active pull-ups and pull-downs compatible with TTL loads.

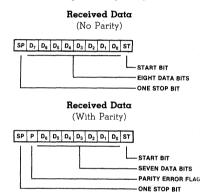

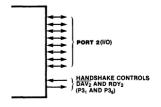

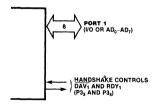

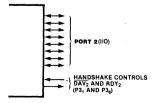

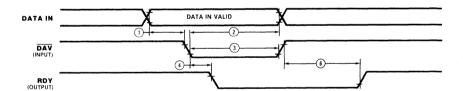

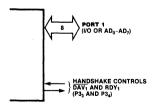

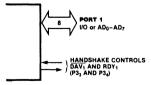

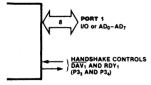

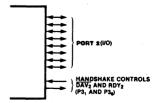

**Port 1** can be programmed as a byte I/O port or as an address/data port for interfacing external memory. When used as an I/O port, Port 1 may be placed under handshake control. In this configuration, Port 3 lines P3<sub>3</sub> and P3<sub>4</sub> are used as the handshake contols RDY<sub>1</sub> and  $\overline{\rm DAV}_1$  (Ready and Data Available).

Memory locations greater than 2048 are referenced through Port 1. To interface external memory, Port 1 must be programmed for the multiplexed Address/Data mode. If more than 256 external locations are required, Port 0 must output the additional lines.

Port 1 can be placed in the high-impedance state along with Port 0,  $\overline{\rm AS}$ ,  $\overline{\rm DS}$  and  $R/\overline{\rm W}$ , allowing the Z8601 to share common resources in multiprocessor and DMA applications. Data transfers can be controlled by assigning P3<sub>3</sub> as a Bus Acknowledge input and P3<sub>4</sub> as a Bus Request output.

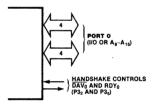

Figure 9a. Port 1

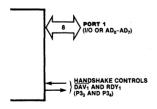

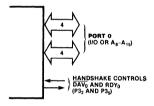

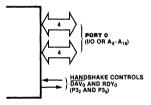

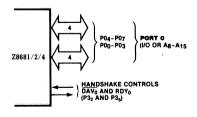

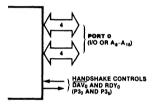

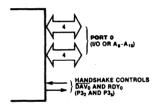

**Port 0** can be programmed as a nibble I/O port, or as an address port for interfacing external memory. When used as an I/O port,

Port 0 may be placed under handshake control. In this configuration, Port 3 lines  $P3_2$  and  $P3_5$  are used as the handshake controls  $\overline{DAV}_0$  and  $RDY_0$ . Handshake signal assignment is dictated by the I/O direction of the upper nibble  $P0_4$ - $P0_7$ .

For external memory references, Port 0 can provide address bits  $A_8\text{-}A_{11}$  (lower nibble) or  $A_8\text{-}A_{15}$  (lower and upper nibble) depending on the required address space. If the address range requires 12 bits or less, the upper nibble of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing. When Port 0 nibbles are defined as address bits, they can be set to the high-impedance state along with Port 1 and the control signals  $\overline{AS}$ ,  $\overline{DS}$  and  $R/\overline{W}$ .

Figure 9b. Port 0

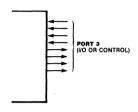

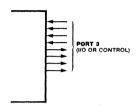

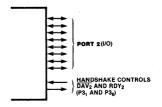

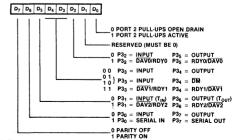

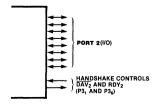

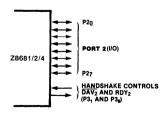

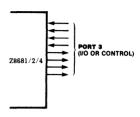

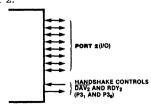

**Port 2** bits can be programmed independently as input or output. The port is always available for I/O operations. In addition, Port 2 can be configured to provide open-drain outputs.

Like Ports 0 and 1, Port 2 may also be placed under handshake control. In this configuration, Port 3 lines P3<sub>1</sub> and P3<sub>6</sub> are

Figure 9c. Port 2

#### I/O Ports (Continued)

used as the handshake controls lines  $\overline{DAV}_2$  and  $RDY_2$ . The handshake signal assignment for Port 3 lines  $P3_1$  and  $P3_6$  is dictated by the direction (input or output) assigned to bit 7 of Port 2.

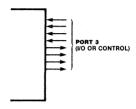

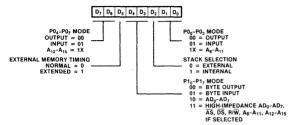

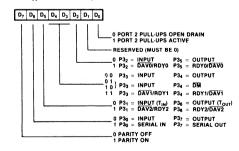

**Port 3** lines can be configured as I/O or control lines. In either case, the direction of the eight lines is fixed as four input (P3<sub>0</sub>-P3<sub>3</sub>) and four output (P3<sub>4</sub>-P3<sub>7</sub>). For serial I/O, lines P3<sub>0</sub> and P3<sub>7</sub> are programmed as serial in and serial out respectively.

Port 3 can also provide the following control functions: handshake for Ports 0, 1 and  $2 (\overline{DAV})$  and RDY); four external

interrupt request signals (IRQ $_0$ -IRQ $_3$ ); timer input and output signals (T $_{IN}$  and T $_{OUT}$ ) and Data Memory Select ( $\overline{DM}$ ).

Figure 9d. Port 3

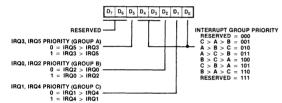

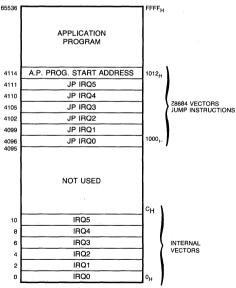

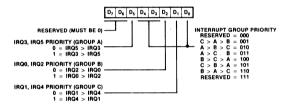

### Interrupts

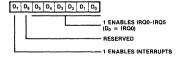

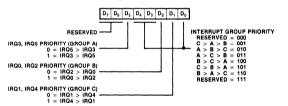

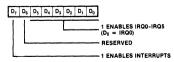

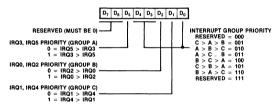

The Z8601 allows six different interrupts from eight sources: the four Port 3 lines P30-P33, Serial In, Serial Out, and the two counter/timers. These interrupts are both maskable and prioritized. The Interrupt Mask register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register.

All Z8601 interrupts are vectored. When an interrupt request is granted, and interrupt machine cycle is entered. This disables all subsequent interrupts, saves the Program Counter and status flags, and branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request.

Polled interrupt systems are also supported. To accommodate a polled structure, any or all of the interrupt inputs can be masked and the Interrupt Request register polled to determine which of the interrupt requests needs service.

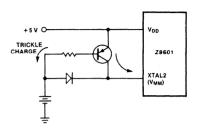

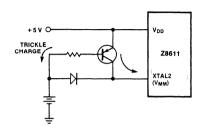

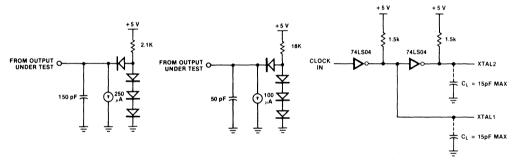

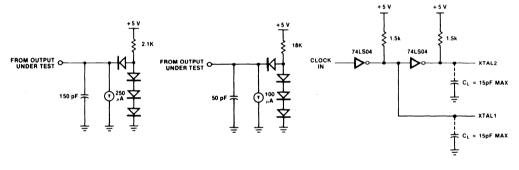

#### Clock

The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal or to any suitable external clock source (XTAL1 = Input, XTAL2 = Output).

The crystal source is connected across XTAL1 and XTAL2, using the recommended

capacitors ( $C_1 \le 15~\mathrm{pF}$ ) from each pin to ground. The specifications for the crystal are as follows:

- AT cut, parallel resonant

- Fundamental types, 8/12 MHz maximum

- Series resistance,  $R_s \leq 100 \Omega$ .

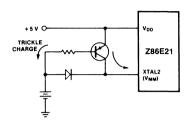

# Power Down Standby Option

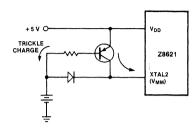

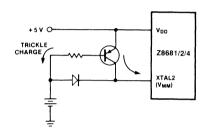

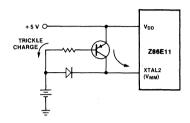

The low-power standby mode allows power to be removed without losing the contents of the 124 general-purpose registers. This mode is available to the user as a bonding option whereby pin 2 (normally XTAL2) is replaced by the  $V_{MM}$  (standby) power supply input. This necessitates the use of an external clock generator (input = XTAL1) rather than a crystal source.

The removal of power, whether intended or due to power failure, must be preceded by a software routine that stores the appropriate status into the register file. Figure 10 shows the recommended circuit for a battery back-up supply system.

Figure 10. Recommended Driver Circuit for Power Down Operation

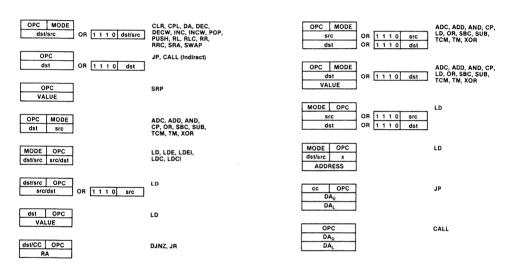

#### Instruction Set Notation

**Addressing Modes.** The following notation is used to describe the addressing modes and instruction operations as shown in the instruction summary.

| IRR | Indirect register pair or indirect working- |

|-----|---------------------------------------------|

|     | register pair address                       |

Symbols. The following symbols are used in

**Symbols.** The following symbols are used in describing the instruction set.

dst Destination location or contents

Assignment of a value is indicated by the symbol "←". For example,

indicates that the source data is added to the destination data and the result is stored in the destination location. The notation "addr(n)" is used to refer to bit "n" of a given location. For example,

refers to bit 7 of the destination operand.

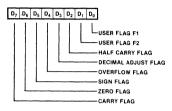

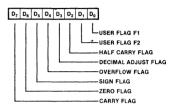

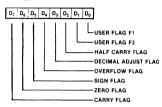

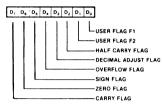

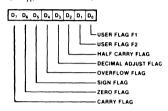

**Flags.** Control Register R252 contains the following six flags:

| Z | Zero flag           | С | Z   | S | V   | D    | Н   | F2  |  |

|---|---------------------|---|-----|---|-----|------|-----|-----|--|

| S | Sign flag           |   |     |   |     |      |     |     |  |

| v | Overflow flag       |   | FI  |   | )   |      |     |     |  |

| D | Decimal-adjust flag |   | F2  |   | {-t | ıser | fla | .gs |  |

| Н | Half-carry flag     |   | 1 4 |   | )   |      |     |     |  |

### Affected flags are indicated by:

0 Cleared to zero

Carry flag

- Set to one

- \* Set or cleared according to operation

- UnaffectedUndefined

# **Condition Codes**

| Value | Mneomonic | Meaning                        | Flags Set               |

|-------|-----------|--------------------------------|-------------------------|

| 1000  |           | Always true                    |                         |

| 0111  | С         | Carry                          | C = 1                   |

| 1111  | NC        | No carry                       | C = 0                   |

| 0110  | Z         | Zero                           | Z = 1                   |

| 1110  | NZ        | Not zero                       | Z = 0                   |

| 1101  | PL        | Plus                           | S = 0                   |

| 0101  | MI        | Minus                          | S = 1                   |

| 0100  | OV        | Overflow                       | V = 1                   |

| 1100  | NOV       | No overflow                    | V = 0                   |

| 0110  | EQ        | Equal                          | Z = 1                   |

| 1110  | NE        | Not equal                      | Z = 0                   |

| 1001  | GE        | Greater than or equal          | (S XOR V) = 0           |

| 0001  | LT        | Less than                      | (S XOR V) = 1           |

| 1010  | GT        | Greater thaN                   | [Z OR (S XOR V)] = 0    |

| 0010  | LE        | Less than or equal             | [Z OR (S XOR V)] = 1    |

| 1111  | UGE       | Unsigned greater than or equal | C = 0                   |

| 0111  | ULT       | Unsigned less than             | C = 1                   |

| 1011  | UGT       | Unsigned greater than          | (C = 0  AND  Z = 0) = 1 |

| 0011  | ULE       | Unsigned less than or equal    | (C OR Z) = 1            |

| 0000  |           | Never true                     |                         |

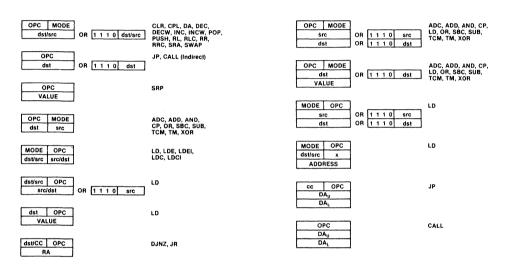

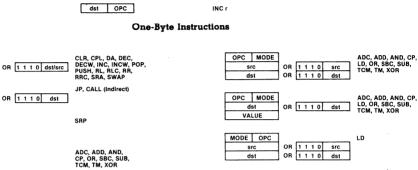

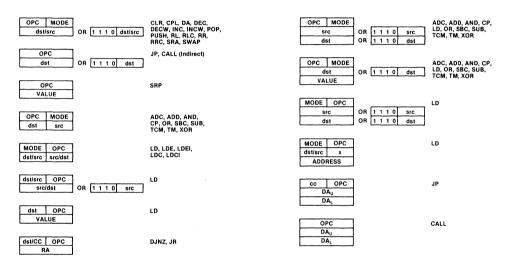

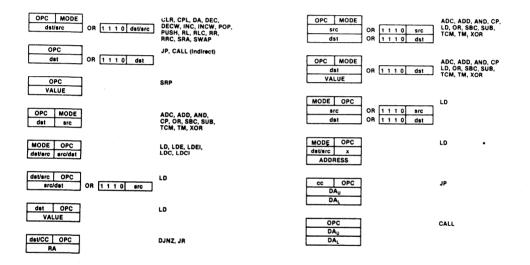

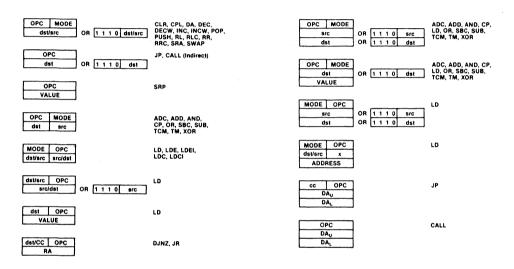

#### Instruction Formats

#### **One-Byte Instructions**

**Two-Byte Instructions**

Three-Byte Instructions

Figure 12. Instruction Formats

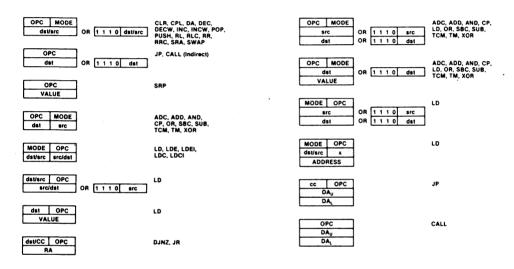

# Instruction Summary

| Instruction                                                                                                 | Addr Mode                | Opcode                  | Flags Affected |   |   |   |   |   |

|-------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|----------------|---|---|---|---|---|

| and Operation                                                                                               | dst src                  | Byte<br>(Hex)           | С              | z | S | V | D | H |

| ADC dst,src<br>dst dst + src + C                                                                            | (Note 1)                 | 10                      | *              | * | * | * | 0 | * |

| <b>ADD</b> dst,src<br>dst ← dst + src                                                                       | (Note 1)                 | 0□                      | *              | * | * | * | 0 | * |

| <b>AND</b> dst,src<br>dst ← dst AND src                                                                     | (Note 1)                 | 5□                      | _              | * | * | 0 | - | - |

| <b>CALL</b> dst<br>SP - SP - 2<br>@SP - PC; PC - d                                                          | DA<br>IRR<br>st          | D6<br>D4                | -              | - |   | _ | - | - |

| CCF<br>C - NOT C                                                                                            |                          | EF                      | *              | - |   | _ | - | - |

| CLR dst<br>dst - 0                                                                                          | R<br>IR                  | B0<br>B1                | _              | _ | - | _ |   | _ |

| <b>COM</b> dst<br>dst ← NOT dst                                                                             | R<br>IR                  | 60<br>61                | _              | * | * | 0 | - | _ |

| CP dst,src<br>dst - src                                                                                     | (Note 1)                 | A□                      | *              | * | * | * | _ | _ |

| <b>DA</b> dst<br>dst ← DA dst                                                                               | R<br>IR                  | 40<br>41                | *              | * | * | Х | _ | _ |

| DEC dst<br>dst dst - 1                                                                                      | R<br>IR                  | 00<br>01                | _              | * | * | * |   | _ |

| <b>DECW</b> dst<br>dst - dst - 1                                                                            | RR<br>IR                 | 80<br>81                | _              | * | * | * | - | - |

| <b>DI</b><br>IMR (7) + 0                                                                                    |                          | 8F                      | _              | _ | _ | _ | _ | _ |

| <b>DJNZ</b> r,dst<br>$r \leftarrow r - 1$<br>if $r \neq 0$<br>PC $\leftarrow$ PC + dst<br>Range: +127, -128 | RA                       | rA<br>r=0-F             | _              |   | _ | _ | _ | _ |

| EI<br>IMR (7) 1                                                                                             |                          | 9F                      | -              |   | - | - | - | - |

| INC dst<br>dst dst + 1                                                                                      | r<br>R<br>IR             | rE<br>r=0-F<br>20<br>21 | -              | * | * | * | - | - |

| INCW dst<br>dst dst + 1                                                                                     | RR<br>IR                 | A0<br>A1                | _              | * | * | * | _ | - |

| IRET<br>FLAGS - @SP; SP<br>PC - @SP; SP - S                                                                 | ← SP + 1<br>P + 2; IMR ( | BF<br>7) — 1            | *              | * | * | * | * | * |

| IP cc,dst<br>if cc is true<br>PC ← dst                                                                      | DA<br>IRR                | cD<br>c=0-F<br>30       | _              | - | - | _ | _ | - |

| JR cc,dst<br>if cc is true,<br>PC - PC + dst<br>Range: +127,-128                                            | RA                       | cB<br>c=0-F             | -              | - | - | _ | - | - |

| Instruction                                       | Addr                    | Mode                     | Opcode                          | Flags Affected |

|---------------------------------------------------|-------------------------|--------------------------|---------------------------------|----------------|

| and Operation                                     | dst                     | STC                      | Byte<br>(Hex)                   | CZSVDH         |

| LD dst,src<br>dst - src                           | r<br>r<br>R             | Im<br>R<br>r             | rC<br>r8<br>r9                  |                |

|                                                   | r<br>X<br>r<br>Ir       | X<br>r<br>Ir<br>r        | r = 0-F<br>C7<br>D7<br>E3<br>F3 |                |

|                                                   | R<br>R<br>R<br>IR<br>IR | R<br>IR<br>Im<br>Im<br>R | E4<br>E5<br>E6<br>E7<br>F5      |                |

| LDC dst,src<br>dst ← src                          | r<br>Irr                | Irr<br>r                 | C2<br>D2                        |                |

| LDCI dst,src<br>dst src<br>r r + 1; rr rr +       | Ir<br>Irr<br>Ir         | Irr<br>Ir                | C3<br>D3                        |                |

| LDE dst,src<br>dst - src                          | r<br>Irr                | Irr<br>r                 | 82<br>92                        |                |

| LDEI dst,src<br>dst ← src<br>r ← r + 1; rr ← rr + | Ir<br>Irr<br>- 1        | Irr<br>Ir                | 83<br>93                        |                |

| NOP                                               | ******                  |                          | FF                              |                |

| OR dst,src<br>dst — dst OR src                    | (No                     | te 1)                    | 4□                              | - * * 0        |

| <b>POP</b> dst<br>dst ← @ SP<br>SP ← SP + 1       | R<br>IR                 |                          | 50<br>51                        |                |

| <b>PUSH</b> src<br>SP - SP - 1; @ SP •            | - src                   | R<br>IR                  | 70<br>71                        |                |

| <b>RCF</b><br>C <b>-</b> 0                        |                         |                          | CF                              | 0              |

| RET<br>PC - @SP; SP - S                           | SP + 2                  |                          | AF                              |                |

| RL dst                                            | J R<br>IR               |                          | 90<br>91                        | * * * *        |

| RLC dst                                           | J R<br>IR               |                          | 10<br>11                        | * * * *        |

| RR dst                                            | □ R<br>IR               |                          | E0<br>E1                        | * * * *        |

| RRC dst                                           | □ R<br>IR               |                          | C0<br>C1                        | * * * *        |

| SBC dst,src<br>dst - dst - src - C                | (No                     | te l)                    | 3□                              | * * * * 1      |

| <b>SCF</b><br>C - 1                               |                         |                          | DF                              | 1              |

| SRA dst                                           | □ R<br>IR               |                          | D0<br>D1                        | * * * 0        |

## Instruction Summary (Continued)

| Instruction                    | Addr I      | Addr Mode Opcode F |               |   | Flags Affected |   |   |   |   |  |  |

|--------------------------------|-------------|--------------------|---------------|---|----------------|---|---|---|---|--|--|

| and Operation                  | dst         | SIC                | Byte<br>(Hex) | С | Z              | s | V | D | H |  |  |

| SRP src<br>RP - src            |             | Im                 | 31            | - | _              | _ | _ | _ | _ |  |  |

| SUB dst,src<br>dst - dst - src | (Note       | 1)                 | 2□            | * | *              | * | * | 1 | * |  |  |

| SWAP dst                       | ⊸ R<br>∍ IB |                    | F0<br>F1      | Х | *              | * | Х | - | - |  |  |

| Instruction                      | Addr | Mode  | Opcode        | Fl | αg | s I | lffe | ecte | əd |

|----------------------------------|------|-------|---------------|----|----|-----|------|------|----|

| and Operation                    | dst  | src   | Byte<br>(Hex) | С  | Z  | S   | V    | D    | H  |

| TCM dst,src<br>(NOT dst) AND src | (No  | te l) | 6□            | -  | *  | *   | 0    | _    | -  |

| TM dst, src<br>dst AND src       | (Not | te l) | 7□            | -  | *  | *   | 0    | -    | -  |

| XOR dst,src<br>dst - dst XOR src | (Not | te l) | В□            | _  | *  | *   | 0    | -    | _  |

#### Note 1

These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a  $\square$  in this table, and its value is found in the following table to the left of the applicable addressing mode pair.

left of the applicable addressing mode pair.

For example, to determine the opcode of an ADC instruction use the addressing modes r (destination) and Ir (source). The result is 13.

| Addr | Mode                    | Lower                              |

|------|-------------------------|------------------------------------|

| dst  | src                     | Opcode Nibble                      |

| r    | r                       | 2                                  |

| r    | Ir                      | 3                                  |

| R    | R                       | 4                                  |

| R    | IR                      | 5                                  |

| R    | IM                      | 6                                  |

| IR   | IM                      | 7                                  |

|      | dst<br>r<br>r<br>R<br>R | r r<br>r Ir<br>R R<br>R IR<br>R IM |

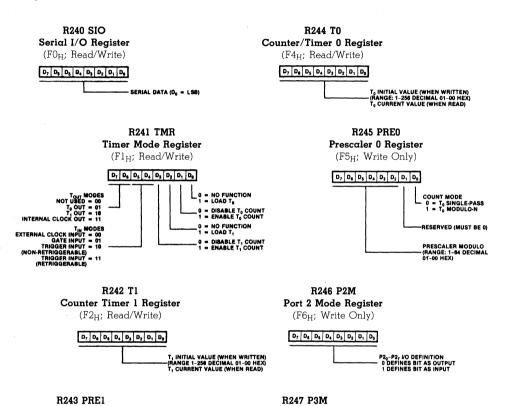

#### Registers

#### R240 SIO Serial I/O Register

(FO<sub>H</sub>; Read/Write)

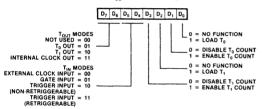

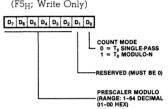

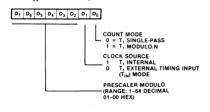

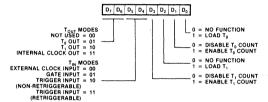

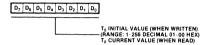

#### R241 TMR

#### Timer Mode Register

(Fl<sub>H</sub>; Read/Write)

#### R242 T1 Counter Timer 1 Register

(F2<sub>H</sub>; Read/Write)

#### R244 T0

#### Counter/Timer 0 Register

(F4H; Read/Write)

#### R245 PRE0

#### Prescaler 0 Register

(F5H; Write Only)

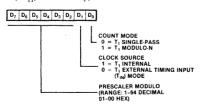

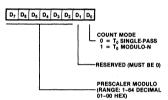

#### R246 P2M Port 2 Mode Register

(F6<sub>H</sub>; Write Only)

#### R243 PRE1

#### Prescaler 1 Register

(F3H; Write Only)

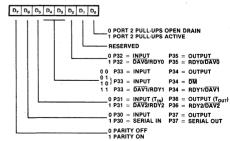

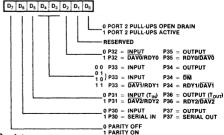

## R247 P3M

#### Port 3 Mode Register

(F7H; Write Only)

Figure 12. Control Registers

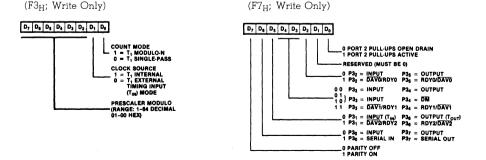

## Registers (Continued)

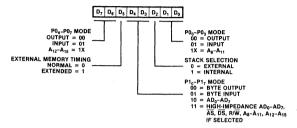

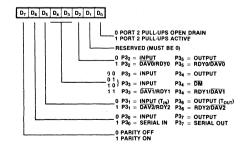

#### R248 P01M Port 0 and 1 Mode Register

(F8<sub>H</sub>; Write Only)

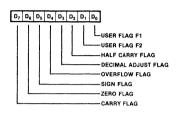

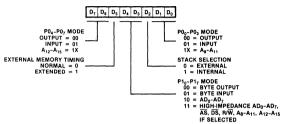

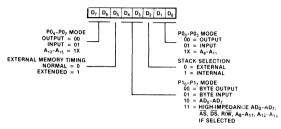

## R252 FLAGS Flag Register

(FC<sub>H</sub>; Read/Write)

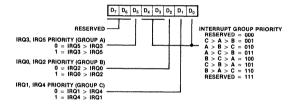

#### R249 IPR

## Interrupt Priority Register

(F9H; Write Only)

#### R253 RP Register Pointer

(FD<sub>H</sub>; Read/Write)

#### **R250 IRQ**

#### Interrupt Request Register

(FAH; Read/Write)

#### R254 SPH

#### Stack Pointer

(FE<sub>H</sub>; Read/Write)

#### **R251 IMR**

#### Interrupt Mask Register

(FB<sub>H</sub>; Read/Write)

#### R255 SPL Stack Pointer

(FF<sub>H</sub>; Read/Write)

Figure 12. Control Registers (Continued)

|   | 0                                  | 1                                    | 2                       | 3                                                     | 4                                                     | 5                                                       | 6                                          | 7                                           | 8                   | 9                                            | Ā                                | В                       | С                          | D                              | E                |

|---|------------------------------------|--------------------------------------|-------------------------|-------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------|----------------------------------------------|----------------------------------|-------------------------|----------------------------|--------------------------------|------------------|

| 0 | 6,5<br>DEC<br>R <sub>1</sub>       | 6,5<br>DEC<br>IR <sub>1</sub>        | 6,5<br>ADD<br>11,12     | 6,5<br><b>ADD</b><br>r <sub>1</sub> , Ir <sub>2</sub> | 10,5<br><b>ADD</b><br>R <sub>2</sub> , R <sub>1</sub> | 10,5<br><b>ADD</b><br>IR <sub>2</sub> , R <sub>1</sub>  | 10,5<br>ADD<br>R <sub>1</sub> , IM         | 10,5<br>ADD<br>IR1, IM                      | 6,5<br>LD<br>r1, R2 | 6,5<br>LD<br>r <sub>2</sub> , R <sub>1</sub> | 12/10,5<br><b>DJNZ</b><br>r1, RA | 12/10,0<br>JR<br>cc, RA | 6,5<br><b>LD</b><br>r1, IM | 12/10,0<br><b>JP</b><br>cc, DA | 6,5<br>INC<br>11 |

| ı | 6,5<br>RLC<br>R <sub>1</sub>       | 6,5<br>RLC<br>IR <sub>1</sub>        | 6,5<br>ADC<br>r1, r2    | 6,5<br>ADC<br>r1, lr2                                 | 10,5<br>ADC<br>R <sub>2</sub> , R <sub>1</sub>        | 10, 5<br>ADC<br>IR <sub>2</sub> , R <sub>1</sub>        | ADC<br>R <sub>1</sub> , IM                 | 10,5<br>ADC<br>IR <sub>1</sub> ,IM          |                     |                                              |                                  |                         |                            |                                |                  |

| 2 | 6,5<br>INC<br>R <sub>1</sub>       | 6,5<br>INC<br>IR <sub>1</sub>        | 6,5<br>SUB<br>11,12     | 6, 5<br>SUB<br>r <sub>1</sub> , Ir <sub>2</sub>       | 10, 5<br>SUB<br>R <sub>2</sub> , R <sub>1</sub>       | 10, 5<br>SUB<br>IR <sub>2</sub> , R <sub>1</sub>        | 10,5<br><b>SUB</b><br>R <sub>1</sub> , IM  | 10, 5<br><b>SUB</b><br>IR <sub>1</sub> , IM |                     |                                              |                                  |                         |                            |                                |                  |

| 3 | 8,0<br>JP<br>IRR1                  | 6, 1<br>SRP<br>IM                    | 6,5<br>SBC<br>r1, r2    | 6, 5<br>SBC<br>r <sub>1</sub> , Ir <sub>2</sub>       | 10,5<br>SBC<br>R <sub>2</sub> , R <sub>1</sub>        | 10, 5<br><b>SBC</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>SBC</b><br>R <sub>1</sub> , IM | 10,5<br>SBC<br>IR <sub>1</sub> , IM         |                     |                                              |                                  |                         |                            |                                |                  |

| 4 | 8,5<br>DA<br>R <sub>1</sub>        | 8,5<br><b>DA</b><br>IR <sub>1</sub>  | 6,5<br>OR<br>r1, r2     | 6, 5<br>OR<br>r1, Ir2                                 | 10,5<br>OR<br>R <sub>2</sub> , R <sub>1</sub>         | 10, 5<br>OR<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>OR<br>R <sub>1</sub> ,IM           | 10,5<br>OR<br>IR <sub>1</sub> , IM          |                     |                                              |                                  |                         |                            |                                |                  |

| 5 | 10,5<br>POP<br>R <sub>1</sub>      | 10,5<br>POP<br>IR <sub>1</sub>       | 6,5<br>AND<br>11,12     | 6, 5<br>AND<br>r1, Ir2                                | 10,5<br>AND<br>R <sub>2</sub> , R <sub>1</sub>        | 10,5<br>AND<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>AND<br>R <sub>1</sub> ,IM          | 10,5<br>AND<br>IR1,IM                       |                     |                                              |                                  |                         |                            |                                |                  |

| 6 | 6,5<br>COM<br>R <sub>1</sub>       | 6,5<br>COM<br>IR <sub>1</sub>        | 6, 5<br>TCM<br>11, 12   | 6, 5<br>TCM<br>r1, Ir2                                | 10,5<br>TCM<br>R <sub>2</sub> , R <sub>1</sub>        | 10,5<br>TCM<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>TCM<br>R <sub>1</sub> ,IM          | 10,5<br>TCM<br>IR1,IM                       |                     |                                              |                                  |                         |                            |                                |                  |

| 7 | 10/12, 1<br>PUSH<br>R <sub>2</sub> | 12/14, 1<br>PUSH<br>IR <sub>2</sub>  | 6, 5<br>TM<br>r1, r2    | 6, 5<br><b>TM</b><br>r1, Ir2                          | 10,5<br>TM<br>R <sub>2</sub> ,R <sub>1</sub>          | 10,5<br>TM<br>IR <sub>2</sub> ,R <sub>1</sub>           | 10, 5<br>TM<br>R <sub>1</sub> , IM         | 10,5<br>TM<br>IR <sub>1</sub> , IM          |                     |                                              |                                  |                         |                            |                                |                  |

| 8 | 10,5<br>DECW<br>RR1                | 10,5<br>DECW<br>IR1                  | 12,0<br>LDE<br>r1,Irr2  | 18,0<br>LDEI<br>Ir1, Irr2                             | 112,111                                               | 21.2,11                                                 | 111, 111                                   | 181,184                                     |                     |                                              |                                  |                         |                            |                                |                  |

| 9 | 6,5<br>RL<br>R1                    | 6,5<br>RL<br>IR1                     | 12,0<br>LDE<br>r2,Irr1  | 18,0<br>LDEI<br>Ir2, Irr1                             |                                                       |                                                         |                                            |                                             |                     |                                              |                                  |                         |                            |                                |                  |

| A | 10,'5<br>INCW<br>RR1               | 10,5<br>INCW<br>IR <sub>1</sub>      | 6,5<br>CP<br>r1, r2     | 6,5<br>CP<br>r1,Ir2                                   | 10, 5<br><b>CP</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br>CP<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>CP<br>R <sub>1</sub> ,IM           | 10,5<br>CP<br>IR1,IM                        |                     |                                              |                                  |                         |                            |                                |                  |

| В | 6,5<br>CLR<br>R <sub>1</sub>       | 6,5<br>CLR<br>IR <sub>1</sub>        | 6,5<br>XOR<br>r1, r2    | 6,5<br>XOR<br>r1, Ir2                                 | 10, 5<br>XOR<br>R <sub>2</sub> , R <sub>1</sub>       | 10,5<br>XOR<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>XOR<br>R <sub>1</sub> , IM         | 10,5<br>XOR<br>IR1,IM                       |                     |                                              |                                  |                         |                            |                                |                  |

| С | 6,5<br>RRC<br>R <sub>1</sub>       | 6,5<br>RRC<br>IR1                    | 12,0<br>LDC<br>r1, Irr2 | 18,0<br>LDCI<br>Ir1,Irr2                              |                                                       |                                                         |                                            | 10,5<br>LD<br>r1, x, R2                     |                     |                                              |                                  |                         |                            |                                |                  |

| D | 6,5<br>SRA<br>Ř <sub>1</sub>       | 6,5<br><b>SRA</b><br>IR <sub>1</sub> | 12,0<br>LDC<br>r2, Irr1 | 18,0<br>LDCI<br>Ir2, Irr1                             | 20,0<br>CALL*                                         |                                                         | 20,0<br>CALL<br>DA                         | 10,5<br>LD<br>r2, x, R1                     |                     |                                              |                                  |                         |                            |                                |                  |

| E | 6, 5<br>RR<br>R <sub>1</sub>       | 6,5<br>RR<br>IR1                     |                         | 6, 5<br>LD<br>r1, lr2                                 | 10,5<br>LD<br>R <sub>2</sub> , R <sub>1</sub>         | 10, 5<br>LD<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>LD<br>R <sub>1</sub> , IM          | 10,5<br>LD<br>IR <sub>1</sub> ,IM           |                     |                                              |                                  |                         |                            |                                |                  |

| F | 8,5<br>SWAP                        | 8,5<br>SWAP                          |                         | 6, 5<br>LD<br>Ir1, r2                                 |                                                       | 10,5<br>LD<br>R <sub>2</sub> , IR <sub>1</sub>          |                                            |                                             |                     |                                              |                                  |                         |                            |                                |                  |

#### Legend:

R = 8-Bit Address r = 4-Bit Address R<sub>1</sub> or r<sub>1</sub> = Dst Address R<sub>2</sub> or r<sub>2</sub> = Src Address

#### Sequence:

Opcode, First Operand, Second Operand

Note: The blank areas are not defined.

## **Absolute Maximum Ratings**

Voltages on all pins with respect to GND ......-0.3 V to +7.0 V Operating Ambient Temperature ...... $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature ..... $-65^{\circ}$ C to  $+150^{\circ}$ C

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

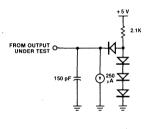

#### Standard Test Conditions

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the reference pin. Standard conditions are as follows:

$$\Box +4.75 \text{ V} \leq \text{V}_{CC} \leq +5.25 \text{ V}$$

☐ GND=0 V

$$\square$$

0°C  $\leq$  T<sub>A</sub>  $\leq$  +70°C

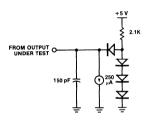

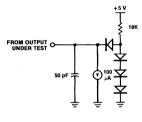

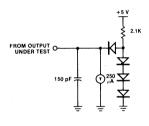

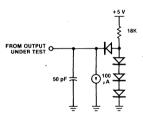

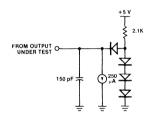

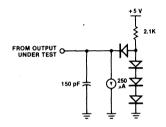

Figure 13. Test Load 1

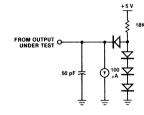

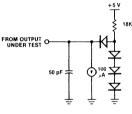

Figure 14. Test Load 2

Figure 15. External Clock Interface Circuit (Both the clock and complement are required)

# DC Characteristics

| Symbol                       | Parameter                      | Min  | Max          | Unit    | Condition                                                     |

|------------------------------|--------------------------------|------|--------------|---------|---------------------------------------------------------------|

| $\overline{v_{\mathrm{CH}}}$ | Clock Input High Voltage       | 3.8  | $v_{\rm CC}$ | V       | Driven by External Clock Generator                            |

| $V_{\rm CL}$                 | Clock Input Low Voltage        | -0.3 | 0.8          | V       | Driven by External Clock Generator                            |

| $v_{IH}$                     | Input High Voltage             | 2.0  | $v_{\rm CC}$ | V       |                                                               |

| $V_{\rm IL}$                 | Input Low Voltage              | -0.3 | 0.8          | V       |                                                               |

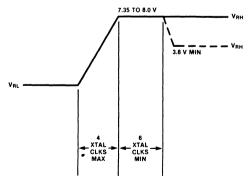

| $V_{RH}$                     | Reset Input High Voltage       | 3.8  | $v_{\rm CC}$ | V       |                                                               |

| $V_{\rm RL}$                 | Reset Input Low Voltage        | -0.3 | 0.8          | V       |                                                               |

| $V_{OH}$                     | Output High Voltage            | 2.4  |              | V       | $I_{OH} = -250 \mu\text{A}$                                   |

| $v_{OL}$                     | Output Low Voltage             |      | 0.4          | V       | $I_{OL} = +2.0 \text{ mA}$                                    |

| $I_{IL}$                     | Input Leakage                  | -10  | 10           | $\mu$ A | $0 \text{ V} \leq \text{ V}_{\text{IN}} \leq +5.25 \text{ V}$ |

| $I_{OL}$                     | Output Leakage                 | -10  | 10           | $\mu$ A | $0 \text{ V} \leq \text{ V}_{\text{IN}} \leq +5.25 \text{ V}$ |

| $I_{IR}$                     | Reset Input Current            |      | - 50         | μA      | $V_{CC} = +5.25 \text{ V}, V_{RL} = 0 \text{ V}$              |

| $I_{CC}$                     | V <sub>CC</sub> Supply Current |      | 120<br>80*   | mA      |                                                               |

| $I_{MM}$                     | V <sub>MM</sub> Supply Current |      | 10           | mA      | Power Down Mode                                               |

| $v_{MM}$                     | Backup Supply Voltage          | 3    | $v_{\rm cc}$ | ٧       | Power Down                                                    |

<sup>\*</sup> This value is for Z8601 only.

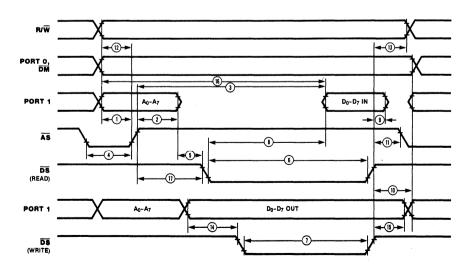

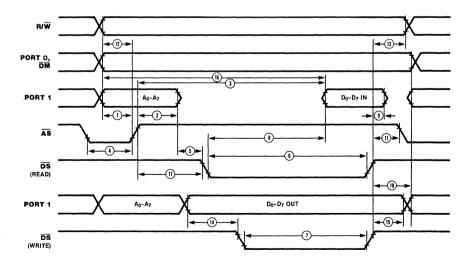

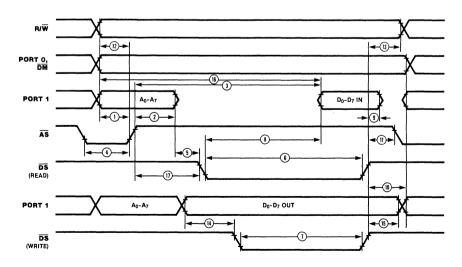

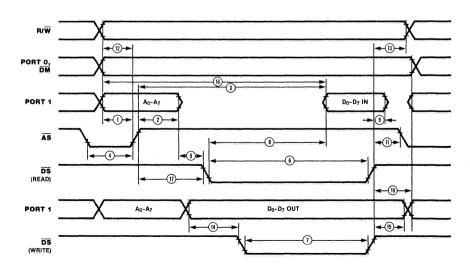

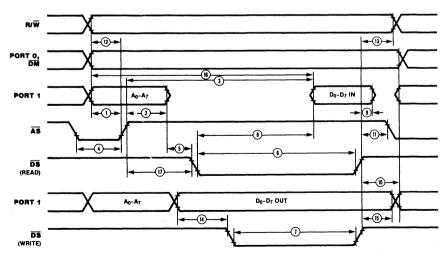

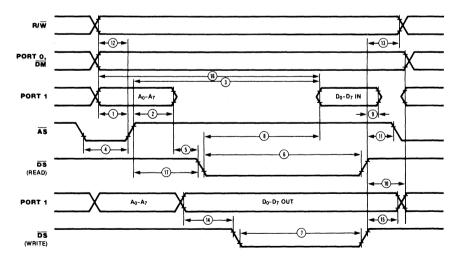

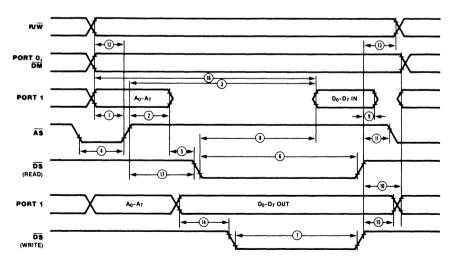

# External I/O or Memory Read and Write Timing

|     |             | ,                                                 | Z86 | 01/L | Z86    | 01A |          |

|-----|-------------|---------------------------------------------------|-----|------|--------|-----|----------|

| No  | Symbol      | Paramter                                          | Min | Max  | Min    | Мах | Notes*†  |

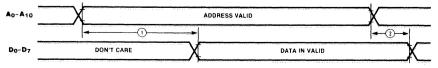

| 1   | TdA(AS)     | Address Valid to <del>AS</del> ↑ Delay            | 50  |      | 35     |     | 1,2,3    |

| 2   | TdAS(A)     | AS ↑ to Address Float Dealy                       | 70  |      | 45     |     | 1,2,3    |

| 3   | TdAS(DR)    | AS ↑ to Read Data Required Valid                  |     | 360  |        | 220 | 1,2,3,4  |

| 4   | TwAS        | AS Low Width                                      | 80  |      | 55     |     | 1,2,3    |

| 5   | TdAz(DS)    | Address Float to <del>DS</del> ↓                  | . 0 |      | 0      |     | 1        |

| 6   | —TwDSR——    | DS (Read) Low Width                               | 250 |      | —185—— |     | -1,2,3,4 |

| 7   | TwDSW       | DS (Write) Low Width                              | 160 |      | 110    |     | 1,2,3,4  |

| 8   | TdDSR(DR)   | DS ↓ to Read Data Required Valid                  |     | 200  |        | 130 | 1,2,3,4  |

| 9   | ThDR(DS)    | Read Data to <del>DS</del> ↑ Hold Time            | 0   |      | 0      |     | 1        |

| 10  | TdDS(A)     | DS ↑ to Address Active Delay                      | 70  |      | 45     |     | 1,2,3    |

| 11  | TdDS(AS)    | DS ↑ to AS ↓ Delay                                | 70  |      | 55     |     | 1,2,3    |

| 12- | -TdR/W(AS)- | —R/W Valid to AS↑ Delay ————                      | 50  |      | 30     |     | - 1,2,3  |

| 13  | TdDS(R/W)   | DS ↑ to R/W Not Valid                             | 60  |      | 35     |     | 1,2,3    |

| 14  | TdDW(DSW)   | Write Data Valid to <del>DS</del> (Write) ↓ Delay | 50  |      | 35     |     | 1,2,3    |

| 15  | TdDS(DW)    | DS ↑ to Write Data Not Valid Delay                | 70  |      | 45     |     | 1,2,3    |

| 16  | TdA(DR)     | Address Valid to Read Data Required Valid         | d   | 410  |        | 255 | 1,2,3,4  |

| 17  | TdAS(DS)    | ĀS↑ to DS↓ Delay                                  | 80  |      | 55     |     | 1,2,3    |

#### NOTES:

- 1. Test Load 1

- 2. Timing numbers given are for minimum TpC.

- 3. Also see clock cycle time dependent characteristics table.

- 4. When using extended memory timing add 2 TpC.

- 5. All timing reference use 2.0 V for a logic «1» and 0.8 V for a logic «0».

- \* All units in nanoseconds (ns).

- † Timings are preliminary and subject to change.

Figure 16. External I/O or Memory Read/Write

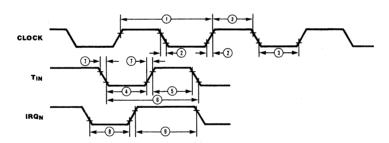

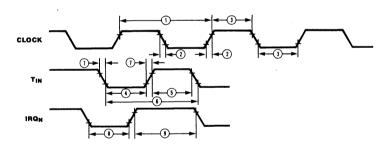

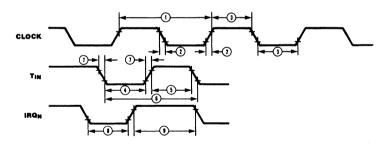

## Additional Timing Table

|    |              |                                   | Z860  | 1/L  | Z8601A |      |         |  |

|----|--------------|-----------------------------------|-------|------|--------|------|---------|--|

| No | Symbol       | Paramter                          | Min   | Max  | Min    | Max  | Notes*† |  |

| 1  | TpC          | Input Clock Period                | 125   | 1000 | 83     | 1000 | 1 :     |  |

| 2  | TrC, TfC     | Clock Input Rise And Fall Times   |       | 25   |        | 15   | 1       |  |

| 3  | TwC          | Input Clock Width                 | 37    |      | 26     |      | 1       |  |

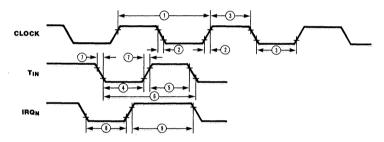

| 4  | TwTinL       | Timer Input Low Width             | 100   |      | 70     |      | 2       |  |

| 5— | —TwTinH——    | —Timer Input High Width———        | 3TpC  |      | 3TpC   |      | 2       |  |

| 6  | TpTin        | Timer Input Period                | 8TpC. |      | 8TpC   |      | 2       |  |

| 7  | TrTin, TfTin | Timer Input Rise And Fall Times   |       | 100  |        | 100  | 2       |  |

| 8a | TwIL         | Interrupt Request Input Low Time  | 100   |      | 70     |      | 2,3     |  |

| 8b | TwIL         | Interrupt Request Input Low Time  | 3TpC  |      | 3TpC   |      | 2,4     |  |

| 9  | TwIH         | Interrupt Request Input High Time | 3TpC  |      | 3TpC   |      | 2,3     |  |

#### NOTES:

- 1. Clock timing references uses 3.8 V for a logic "l" and 0.8 V for a logic "0".

- 2. Timing reference uses 2.0 V for a logic "l" and 0.8 V for a logic "0".

- 3. Interrupt request via Port 3 (P3<sub>1</sub>-P3<sub>3</sub>).

- 4. Interrupt request via Port 3 (P3<sub>0</sub>).

- \* Units in nanoseconds (ns).

- † Timings are preliminary and subject to change.

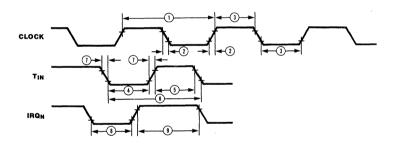

Figure 17. Additional Timing

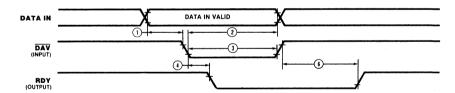

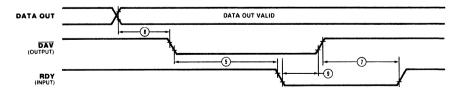

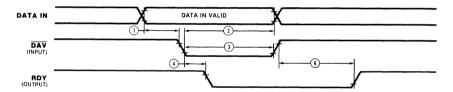

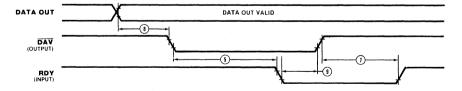

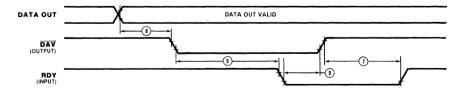

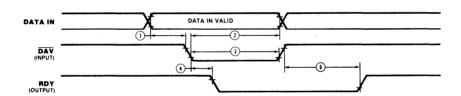

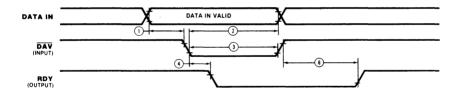

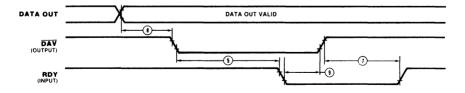

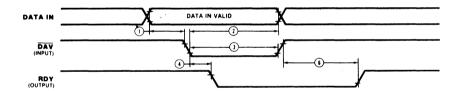

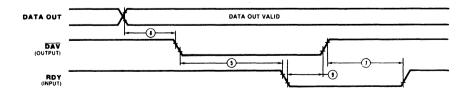

#### Handshake Timing

|    |                |                                             | Z86 | Z8601A |     |     |         |

|----|----------------|---------------------------------------------|-----|--------|-----|-----|---------|

| No | Symbol         | Paramter                                    | Min | Max    | Min | Мах | Notes*† |

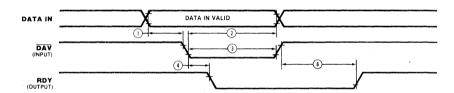

| 1  | TsDI(DAV)      | Data In Setup Time                          | 0   |        | 0   | _   |         |

| 2  | ThDI(DAV)      | Data In Hold Time                           | 230 |        | 160 |     |         |

| 3  | TwDAV          | Data Available Width                        | 175 |        | 120 |     |         |

| 4  | TdDAVIf(RDY)   | DAV ↓ Input to RDY ↓ Delay                  |     | 175    |     | 120 | 1,2     |

| 5— | -TdDAVOf(RDY)- | — <del>DAV</del> ↓ Output to RDY ↓ Delay——— | 0   |        | 0   |     | 1,3     |

| 6  | TdDAVIr(RDY)   | DAV ↑ Input to RDY ↑ Delay                  |     | 175    |     | 120 | 1,2     |

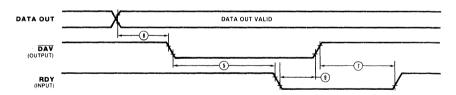

| 7  | TdDAV0r(RDY)   | DAV ↑ Output to RDY ↑ Delay                 | 0   |        | 0   |     | 1,3     |

| 8  | TdDO(DAV)      | Data Out to <del>DAV</del> ↓ Delay          | 50  |        | 30  |     | l       |

| 9  | TdRDY(DAV)     | Rdy ↓ Input to DAV ↑ Delay                  | 0   | 200    | 0   | 140 | 1       |

#### NOTES:

- 1. Test Load 1

- 2. Input handshake

3. Output handshake

- 4. All timing regerences use 2.0 V for a logic "1" and 0.8 V for a logic "0".

- Units in nanoseconds (ns).

- † Timings are preliminary and subject to change.

Figure 18. Input Handshake

Figure 19. Output Handshake

# Clock-Cycle-Time-Dependent Characteristics

|        |           | Z8601/L   | Z8601A    |

|--------|-----------|-----------|-----------|

| Number | Symbol    | Equation  | Equation  |

| 1      | TdA(AS)   | TpC-75    | TpC-50    |

| 2      | TdAS(A)   | TpC-55    | TpC-40    |

| 3      | TdAS(DR)  | 4TpC-140* | 4TpC-110* |

| 4      | TwAS      | TpC-45    | TpC-30    |

| 6 ———  | TwDSR     | 3TpC-125* | 3TpC-65*  |

| 7      | TwDSW     | 2TpC-90*  | 2TpC-55*  |

| 8      | TdDSR(DR) | 3TpC-175* | 3TpC-120* |

| . 10   | Td(DS)A   | TpC-55    | TpC-40    |

| 11     | TdDS(AS)  | TpC-55    | TpC-30    |

| 12     | TdR/W(AS) | TpC-75    | TpC-55    |

| 13     | TdDS(R/W) | TpC-65    | TpC-50    |

| 14     | TdDW(DSW) | TpC-75    | TpC-50    |

| 15     | TdDS(DW)  | TpC-55    | TpC-40    |

| 16     | TdA(DR)   | 5TpC-215* | 5TpC-160* |

| 17     | TdAS(DS)  | TpC-45    | TpC-30    |

<sup>\*</sup> Add 2TpC when using extended memory timing

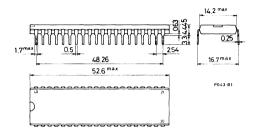

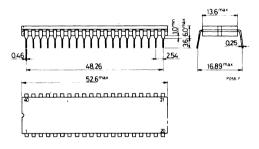

# Ordering Information

| Туре      | Package              | Temp.     | Clock   | Description          |

|-----------|----------------------|-----------|---------|----------------------|

| Z8601 B1  | Plastic              | 0/+70°C \ |         | 2K ROM Microcomputer |

| Z8601 B6  | Plastic              | −40/+85°C |         |                      |

| Z8601 D1  | Ceramic              | 0/+70°C   |         |                      |

| Z8601 D6  | Ceramic              | −40/+85°C | 8 MHz   |                      |

| Z8601 C1  | Plastic Chip Carrier | 0/+70°C   | O MILIZ |                      |

| Z8601 C6  | Plastic Chip Carrier | -40/+85°C |         |                      |

| Z8601 K1  | Ceramic Chip Carrier | 0/+70°C   |         |                      |

| Z8601 K6  | Ceramic Chip Carrier | −40/+85°C |         |                      |

| Z8601A B1 | Plastic              | 0/+70°C   |         |                      |

| Z8601A B6 | Plastic              | -40/+85°C |         |                      |

| Z8601A D1 | Ceramic              | 0/+70°C   |         |                      |

| Z8601A D6 | Ceramic              | -40/+85°C | 10 MII  |                      |

| Z8601A C1 | Plastic Chip Carrier | 0/+70°C   | 12 MHz  |                      |

| Z8601A C6 | Plastic Chip Carrier | -40/+85°C |         |                      |

| Z8601A K1 | Ceramic Chip Carrier | 0/+70°C   |         |                      |

| Z8601A K6 | Ceramic Chip Carrier | -40/+85°C |         |                      |

| Z8601L B1 | Plastic              | 0/+70°C   |         | 2K ROM Microcomputer |

| Z8601L B6 | Plastic ·            | -40/+85°C |         | Low Power version    |

| Z8601L D1 | Ceramic              | 0/+70°C   |         |                      |

| Z8601L D6 | Ceramic              | -40/+85°C | 0.1411  |                      |

| Z8601L C1 | Plastic Chip Carrier | 0/+70°C   | 8 MHz   |                      |

| Z8601L C6 | Plastic Chip Carrier | -40/+85°C |         |                      |

| Z8601L K1 | Ceramic Chip Carrier | 0/+70°C   |         |                      |

| Z8601L K6 | Ceramic Chip Carrier | -40/+85°C |         |                      |

# **Z8 4K ROM Microcomputer**

- Complete microcomputer, 4K bytes of ROM, 128 bytes of RAM, 32 I/O lines, and up to 60K bytes addressable external space each for program and data memory.

- 144-byte register file, including 124 general-purpose registers, four I/O port registers, and 16 status and control registers.

- Minimum instruction execution time 1 μs at 12 MHz.

- Vectored, priority interrupts for I/O, counter/timers, and UART.

- Full-duplex UART and two programmable 8-bit counter/timers, each with a 6-bit programmable prescaler.

- Register Pointer so that short, fast instructions can access any of nine working register groups in 1 μs.

- On-chip oscillator which accepts crystal or external clock drive.

- Low-power standby option that retains contents of general-purpose registers.

- Single +5 V power supply—all pins TTL-compatible.

- Low Power version (Z8611L):

- Available 8 MHz

- Current consumption 80 mA

- Available in 8 and 12 MHz versions.

# General Description

The Z8611 microcomputer introduces a new level of sophistication to single-chip architecture. Compared to earlier single-chip microcomputers, the Z8611 offers faster execution; more efficient use of memory; more sophisticated interrupt, input/output and bit-manipulation capabilities; and easier system expansion.

Under program control, the Z8611 can be

tailored to the needs of its user. It can be configured as a stand-alone microcomputer with 4K bytes of internal ROM, a traditional microprocessor that manages up to 120K bytes of external memory, or a parallel-processing element in a system with other processors and peripheral controllers linked by the Z-BUS. In all configurations, a large number of pins remain available for I/O.

Figure 1. Logic Functions

# General Description (Continued)

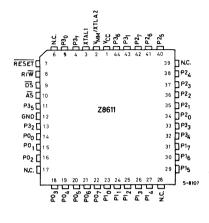

Figure 2. Pin Configuration

N.C. . NO CONNECTION

Figure 2a. Chip Carrier Pin Configuration

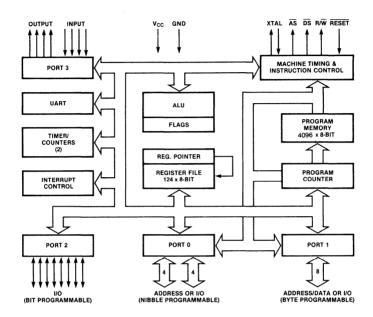

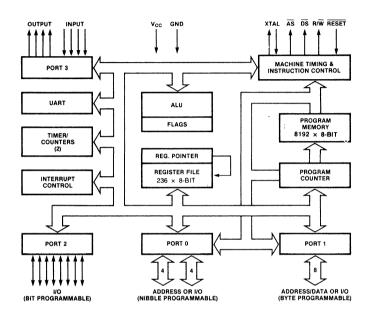

#### Architecture

Z8611 architecture is characterized by a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features that are helpful in many applications.

Microcomputer applications demand powerful I/O capabilities. The Z8611 fulfills this with 32 pins dedicated to input and output. These lines are grouped into four ports of eight lines each and are configurable under software control to provide timing, status signals, serial or parallel I/O with or without handshake, and an address/data bus for interfacing external memory.

Because the multiplexed address/data bus is merged with the I/O-oriented ports, the Z8611 can assume many different memory and I/O configurations. These configurations

range from a self-contained microcomputer to a microprocessor that can address 120K bytes of external memory (Figure 3).

Three basic address spaces are available to support this wide range of configurations: program memory (internal and external), data memory (external) and the register file (internal). The 144-byte random-access register file is composed of 124 general-purpose registers, four I/O port registers, and 16 control and status registers.

To unburden the program from coping with real-time problems such as serial data communication and counting/timing, an asynchronous receiver/transmitter (UART) and two counter/timers with a large number of user-selectable modes are offered on-chip. Hardware support for the UART is minimized because one of the on-chip timers supplies the bit rate.

# Architecture (Continued)

Figure 3. Functional Block Diagram

# Pin Description

**AS.** Address Strobe (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Addresses output via Port 1 for all external program or data memory transfers are valid at the trailing edge of  $\overline{AS}$ . Under program control,  $\overline{AS}$  can be placed in the high-impedance state along with Ports 0 and 1, Data Strobe and Read/Write.

**DS.** Data Strobe (output, active Low). Data Strobe is activated once for each external memory transfer.

**P0<sub>0</sub>-P0<sub>7</sub>.** I/O Port Lines (input/output, TTL compatible). 8 lines Nibble Programmable that can be configured under program control for I/O or external memory interface.

**Pl<sub>0</sub>-Pl<sub>7</sub>.** I/O Port Lines (input/output, TTL compatible). 8 lines Byte Programmable that can be configured under program control for I/O or multiplexed address  $(A_0-A_7)$  and data  $(D_0-D_7)$  lines used to interface with program/data memory.

**P2<sub>0</sub>-P2<sub>7</sub>.** I/O Port Lines (input/output, TTL compatible). 8 lines Bit Programmable. In addition they can be configured to provide open-drain output.

**P30-P34.** Input Port Lines (TTL compatible). They can also configured as control lines.

**P3<sub>5</sub>-P3<sub>7</sub>.** Output Port Lines (TTL compatible). They can also configured as control lines.

# \$\$\$ Z8611/L

# Pin Description (Continued)

**RESET.** Reset (input, active Low). RESET initializes the Z8611. When RESET is deactivated, program execution begins from internal program location 000C<sub>H</sub>.

$\mathbf{R}/\overline{\mathbf{W}}$ . Read/Write (output). R/ $\overline{\mathbf{W}}$  is Low when the Z8611 is writing to external program or data memory.

**XTAL1, XTAL2.** Crystol 1, Crystal 2 (time-base input and output). These pins connect a parallel-resonant crystal (8 or 12 MHz maximum) or an external single-phase clock (8 or 12 MHz maximum) to the on-chip clock oscillator and buffer.

# **Address Spaces**

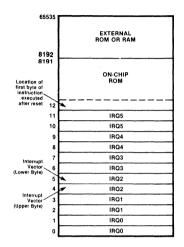

**Program Memory.** The 16-bit program counter addresses 64K bytes of program memory space. Program memory can be located in two areas: one internal and the other external (Figure 4). The first 4096 bytes consist of on-chip mask-programmed ROM. At addresses 4096 and greater, the Z8611 executes external program memory fetches.

The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts.

**Data Memory.** The Z8611 can address 60K bytes of external data memory beginning at location 4096 (Figure 5). External data memory may be included with or separated from the external program memory space.  $\overline{\rm DM}$ , an optional I/O function that can be programmed to appear on pin P34, is used to distinguish between data and program memory space.

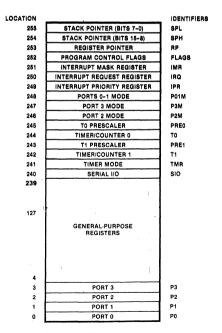

Register File. The 144-byte register file includes four I/O port registers (R0-R3), 124

general-purpose registers (R4-R127) and 16 control and status registers (R240-R255). These registers are assigned the address locations shown in Figure 6.

Z8611 instructions can access registers directly or indirectly with an 8-bit address field. The Z8611 also allows short 4-bit register addressing using the Register Pointer (one of the control registers). In the 4-bit mode, the register file is divided into nine working-register groups, each occupying 16 contiguous locations (Figure 7). The Register Pointer addresses the starting location of the active working-register group.

**Stacks.** Either the internal register file or the external data memory can be used for the stack. A 16-bit Stack Pointer (R254 and R255) is used for the external stack, which can reside anywhere in data memory between locations 4096 and 65535. An 8-bit Stack Pointer (R255) is used for the internal stack that resides within the 124 general-purpose registers (R4-R127).

# Address Spaces (Continued)

Figure 4. Program Memory Map

Figure 6. The Register File

Figure 5. Data Memory Map

Figure 7. The Register Pointer

# Serial Input/Output